Peripherals Routed Through the DPI

A-240 ADSP-214xx SHARC Processor Hardware Reference

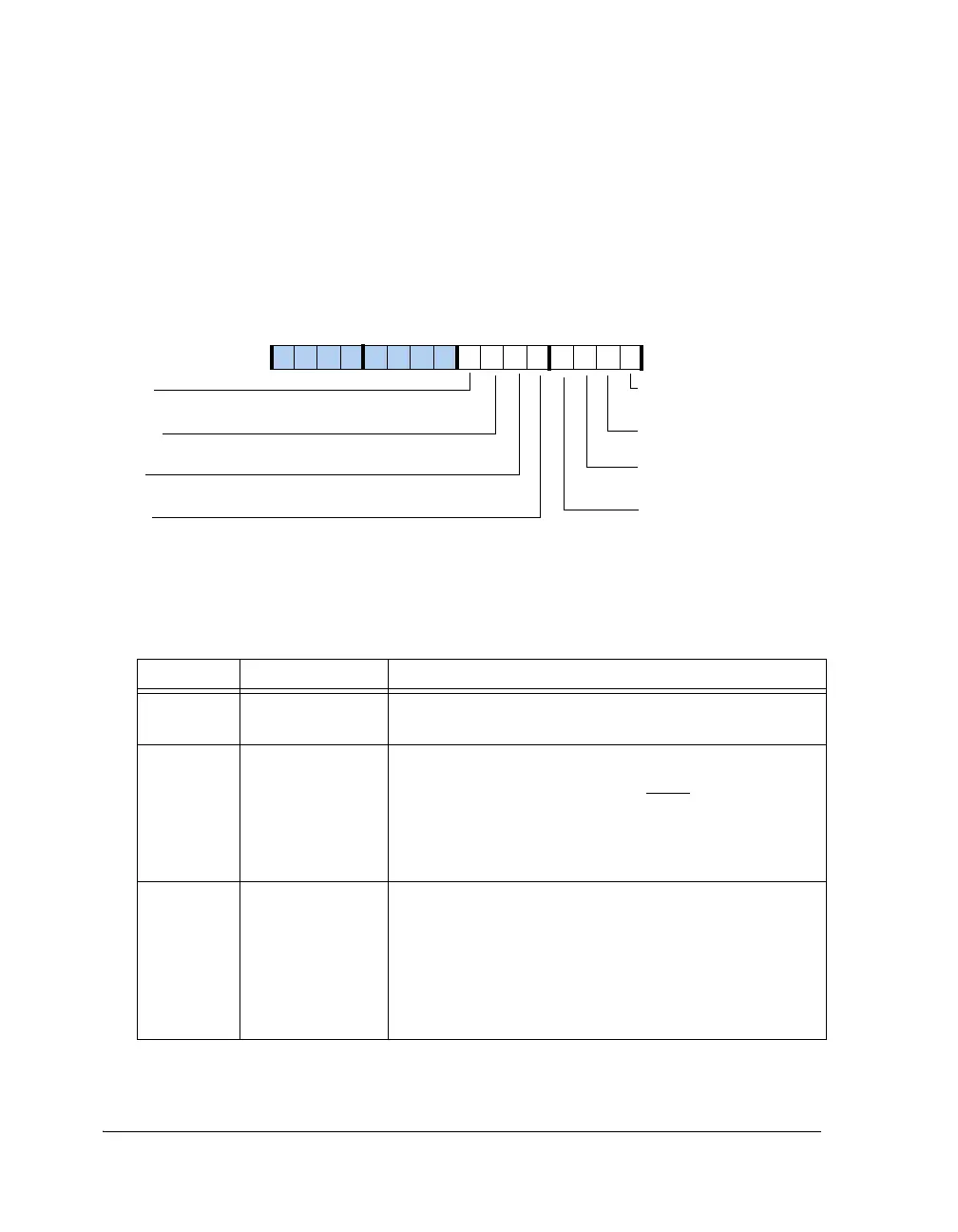

Status (SPISTAT, SPISTATB) Registers

The

SPISTAT and SPISTATB registers are used to detect when an SPI trans-

fer is complete, if transmission/reception errors occur, and the status of

the TXSPI and RXSPI FIFOs. The bit settings for these registers are shown

in Figure A-134 and described in Table A-125.

Figure A-134. SPISTAT, SPISTATB Registers

Table A-125. SPISTAT Register Bit Descriptions (RO)

Bit Name Description

0 (RO) SPIF SPI Transmit or Receive Transfer Complete. SPIF is set

when an SPI single-word transfer is complete.

1 (W1C) MME Multimaster Error or Mode-Fault Error. MME is set in a

master device when some other device tries to become the

master. In multimaster mode, if the

SPIDS input signal of a

master is asserted (low) an error has occurred. This means

that another device is also trying to be the master. Clears the

SPIMME bit.

2 (W1C) TUNF Transmission Error. TUNF is set when transmission occurred

with no new data in TXSPI register.

The TUNF bit (2) is set when all of the conditions of trans-

mission are met and there is no new data in TXSPI (TXSPI is

empty). In this case, the transmission contents depend on the

state of the SENDZ bit in the SPICTL register. Clears the

SPIUNF bit.

TXCOL

SPIF

SPI Transaction Complete

MME

Multimaster Error

Transmit Collision Error

RXS

TXSPI Data Buffer Status

ROVF

Reception Error (Overflow)

TUNF

Transmission Error (Underflow)

TXS

RXSPI Data Buffer Status

SPIFE

External Transaction Complete

09 837564 2114 12 11 101315

Loading...

Loading...