ADSP-214xx SHARC Processor Hardware Reference 21-21

Two Wire Interface Controller

Master Mode Clock Setup

Master mode operation is set up and executed on a per-transfer basis. An

example of programming steps for a receive and for a transmit are given

separately in following sections. The clock setup programming step listed

here is common to both transfer types.

Program the TWIDIV register. This defines the clock high duration and

clock low duration.

Master Mode Transmit

Follow these programming steps for a single master mode transmit:

1. Program the

TWIMADDR register. This defines the address transmit-

ted during the address phase of the transfer.

2. Program the

TXTWI8 or TXTWI16 registers. This is the initial data

transmitted. It is considered an error to complete the address phase

of the transfer and not have data available in the transmit FIFO

buffer.

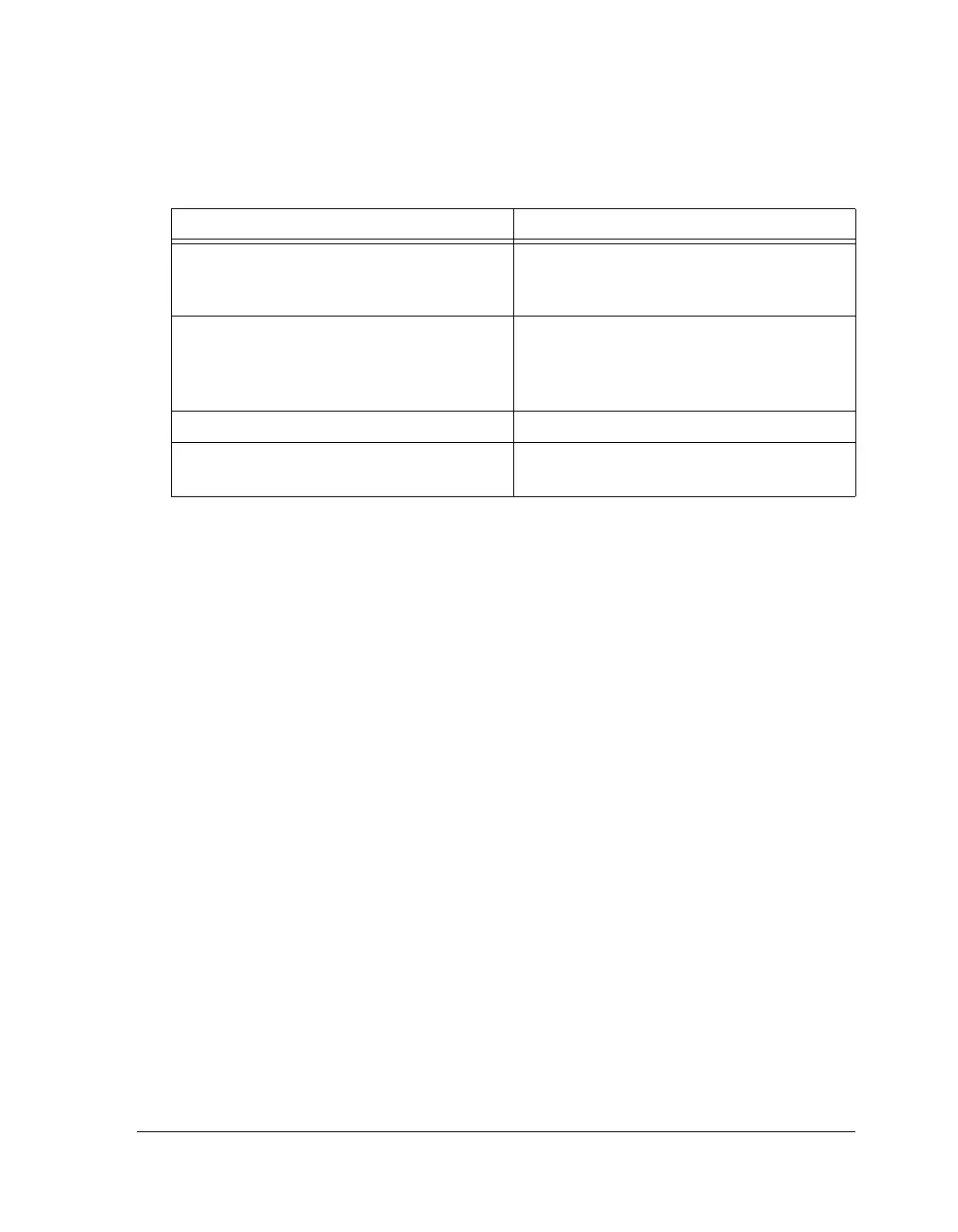

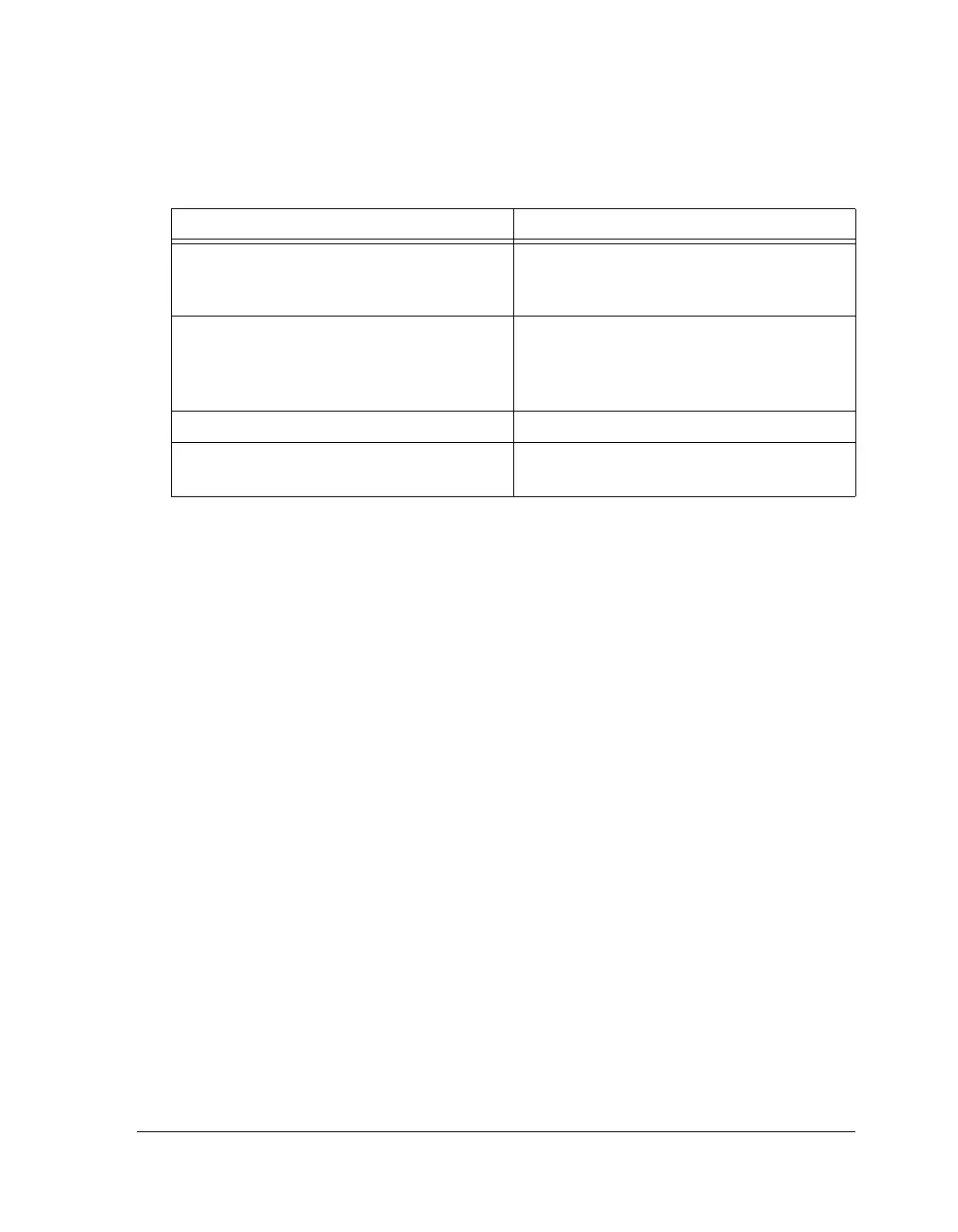

Table 21-5. Slave Mode Setup Interaction (Slave Addressed as Receiver)

TWI Controller Master Processor

Interrupt: TWISINIT – Slave transfer has been

initiated.

Change on the next sides always.

Interrupt Acknowledge: W1C the TWIIRPTL

register.

Interrupt: TWIRXS – Receive buffer has 1 or 2

bytes (according to TWIRXINT).

Read receive FIFO buffer.

Change on the next sides always.

Interrupt Acknowledge: W1C the TWIIRPTL

register

... ...

Interrupt: TWISCOMP – Slave transfer com-

plete.

Read receive FIFO buffer.

Acknowledge: Clear interrupt source bits.

Loading...

Loading...