SDRAM Controller (ADSP-2147x/ADSP-2148x)

3-36 ADSP-214xx SHARC Processor Hardware Reference

Multi Bank Operation with Data Packing

A logical address corresponds to 2 physical addresses when X16DE = 1.

Consequently a physical address (for example of 512 x 16 page size) trans-

lates into a logical address of 256 x 16 words to satisfy the packing.

According to this all row addresses are shifted by 2.

A populated SDRAM of 2M x 16 x 4 with a 512 word page size, con-

nected to external bank 0 and using bank interleaving (SDADDRMODE bit =

0) has the following logical map:

0x200000 logical start address int bankA

0x2000FF logical end address int bankA

0x300000 logical start address int bankB

0x3000FF logical end address int bankB

0x400000 logical start address int bankC

0x4000FF logical end address int bankC

0x500000 logical start address int bankD

0x5000FF logical end address int bankD

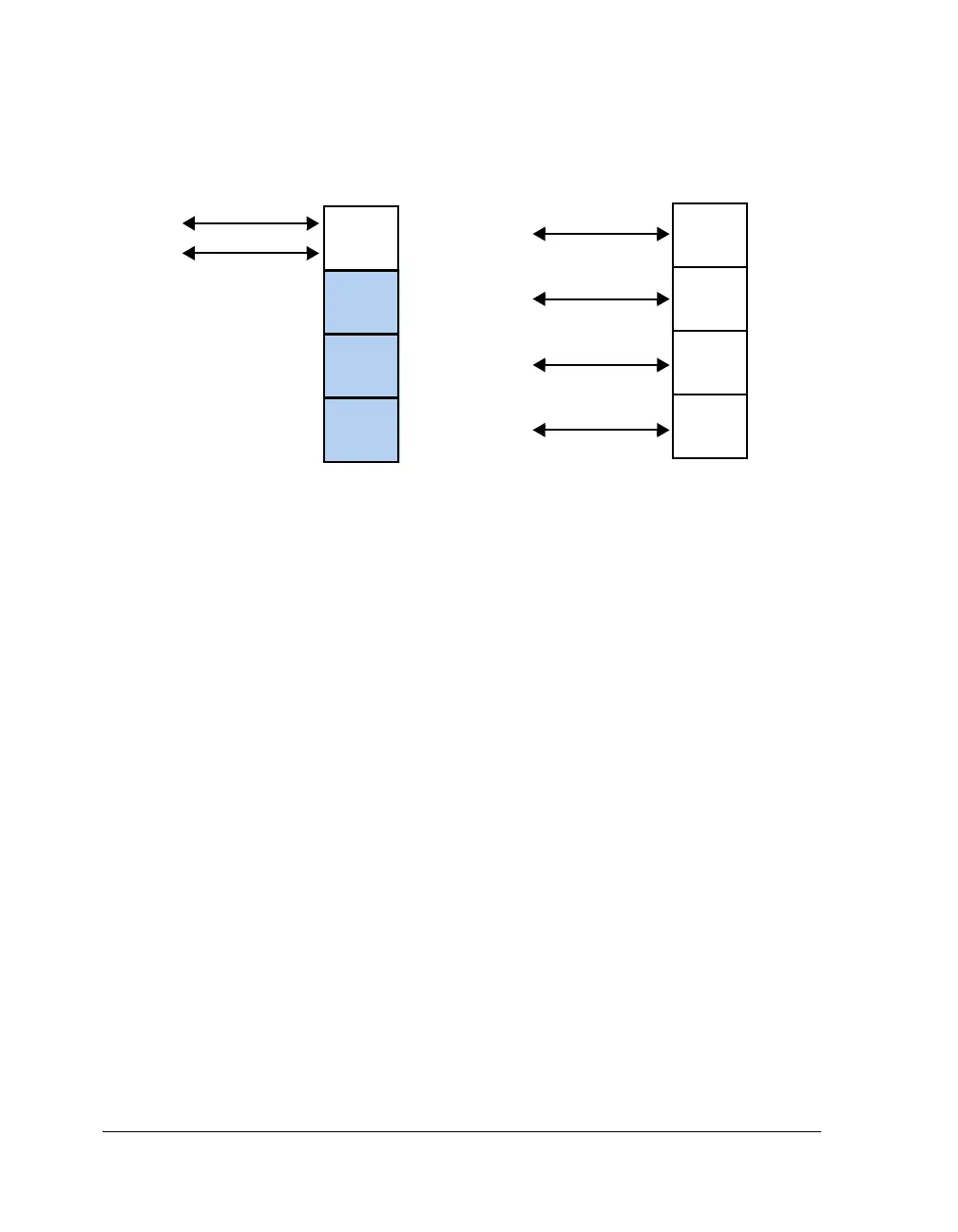

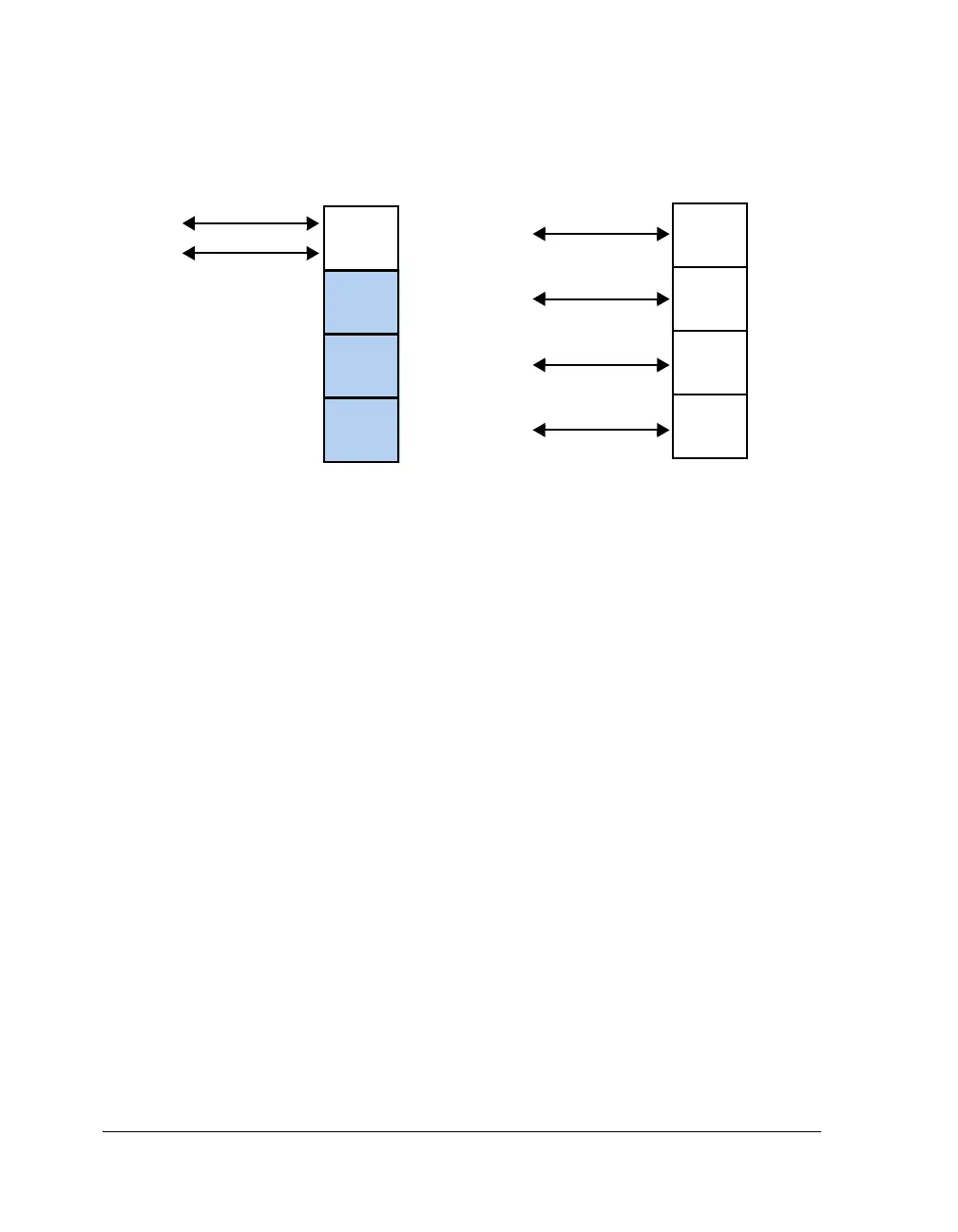

Figure 3-8. Single Versus Multibank Access

Bank A

Bank B

Bank C

Bank D

Bank A

Bank B

Bank C

Bank D

Access to page x

Access to page y

Access to page x

Access to page y

Access to page x

Access to page y

Single bank access Multibank access

Loading...

Loading...