Peripherals Routed Through the DPI

A-260 ADSP-214xx SHARC Processor Hardware Reference

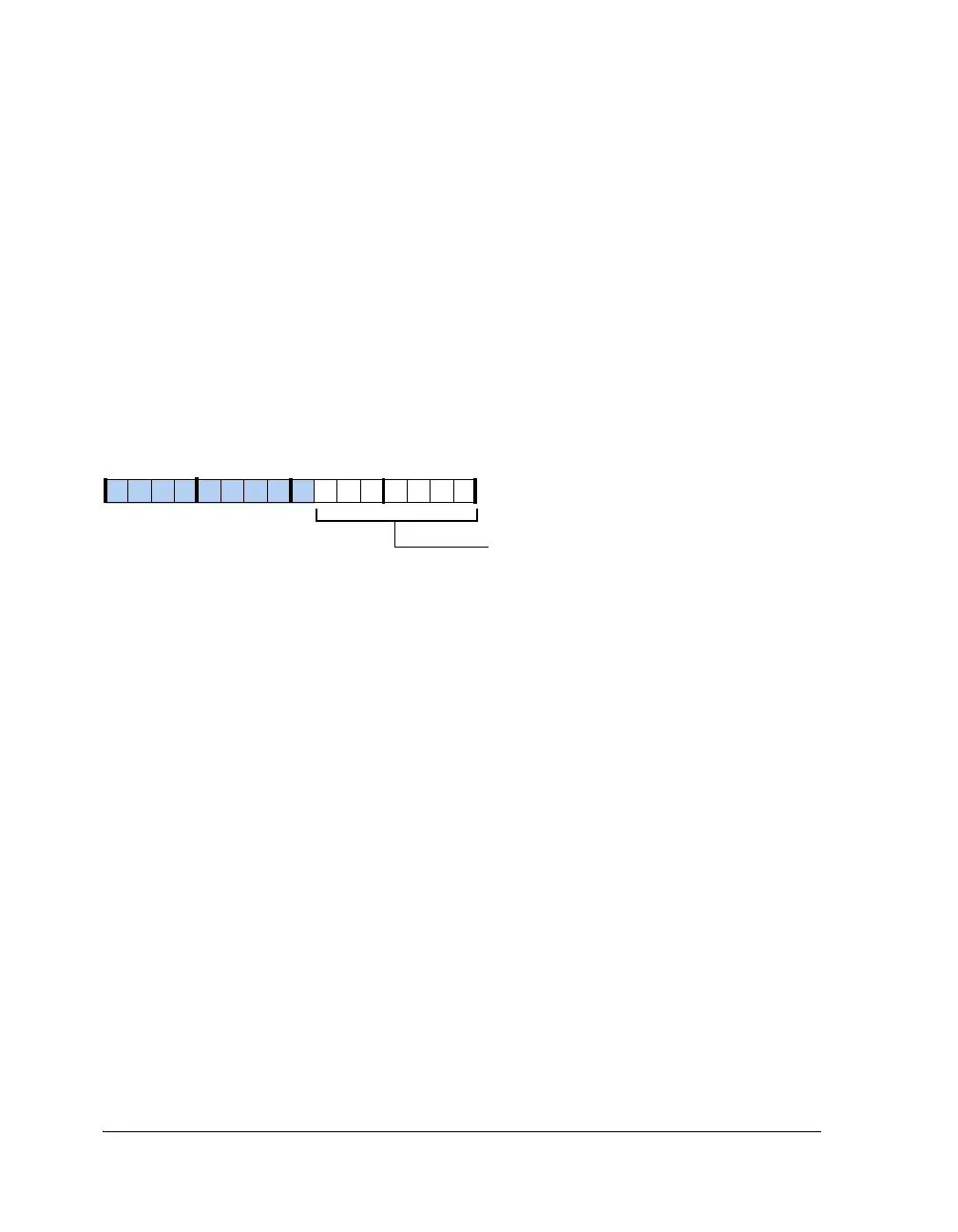

Master Address Register (TWIMADDR)

During the addressing phase of a transfer, the TWI controller, with its

master enabled, transmits the contents of the TWI master mode address

register (

TWIMADDR, shown in Figure A-149). When programming this reg-

ister, omit the read/write bit. That is, only the upper 7 bits that make up

the slave address should be written to this register. For example, if the

slave address is 1010000X, then TWIMADDR is programmed with 1010000,

which corresponds to 0x50. When sending out the address on the bus, the

TWI controller appends the read/write bit as appropriate, based on the

state of the MDIR bit in the master mode control register.

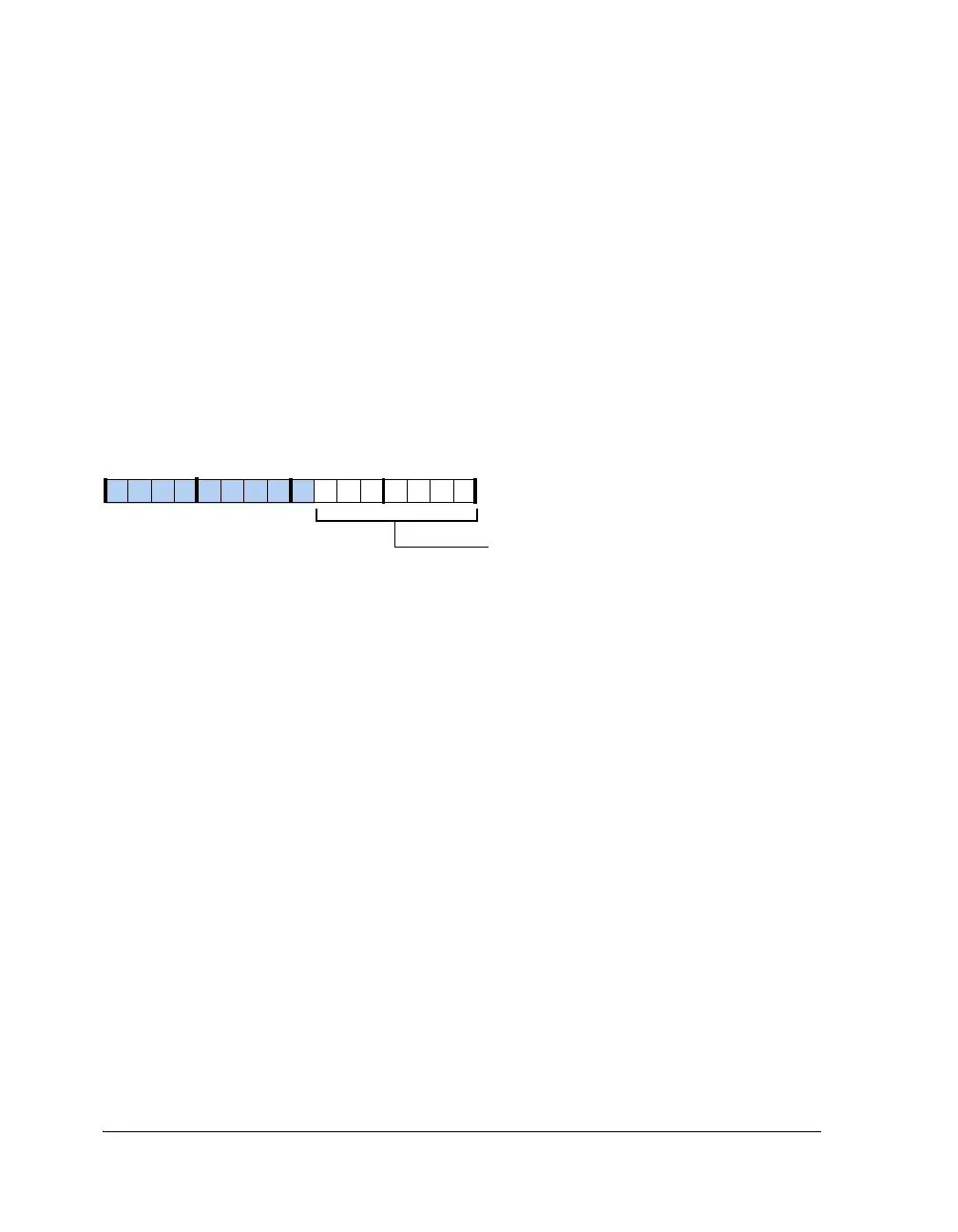

Master Status Register (TWIMSTAT)

The TWI master mode status register (TWIMSTAT, shown in Figure A-150

and described in Table A-141) holds information during master mode

transfers and at their conclusions. Generally, master mode status bits are

not directly associated with the generation of interrupts but offer informa-

tion on the current transfer. Slave mode operation does not affect master

mode status bits.

Figure A-149. TWIMADDR Register (RW)

MADDR (6–0)

Master Mode Address

09 837564 2114 12 11 101315

Loading...

Loading...