operation.

1/f

s

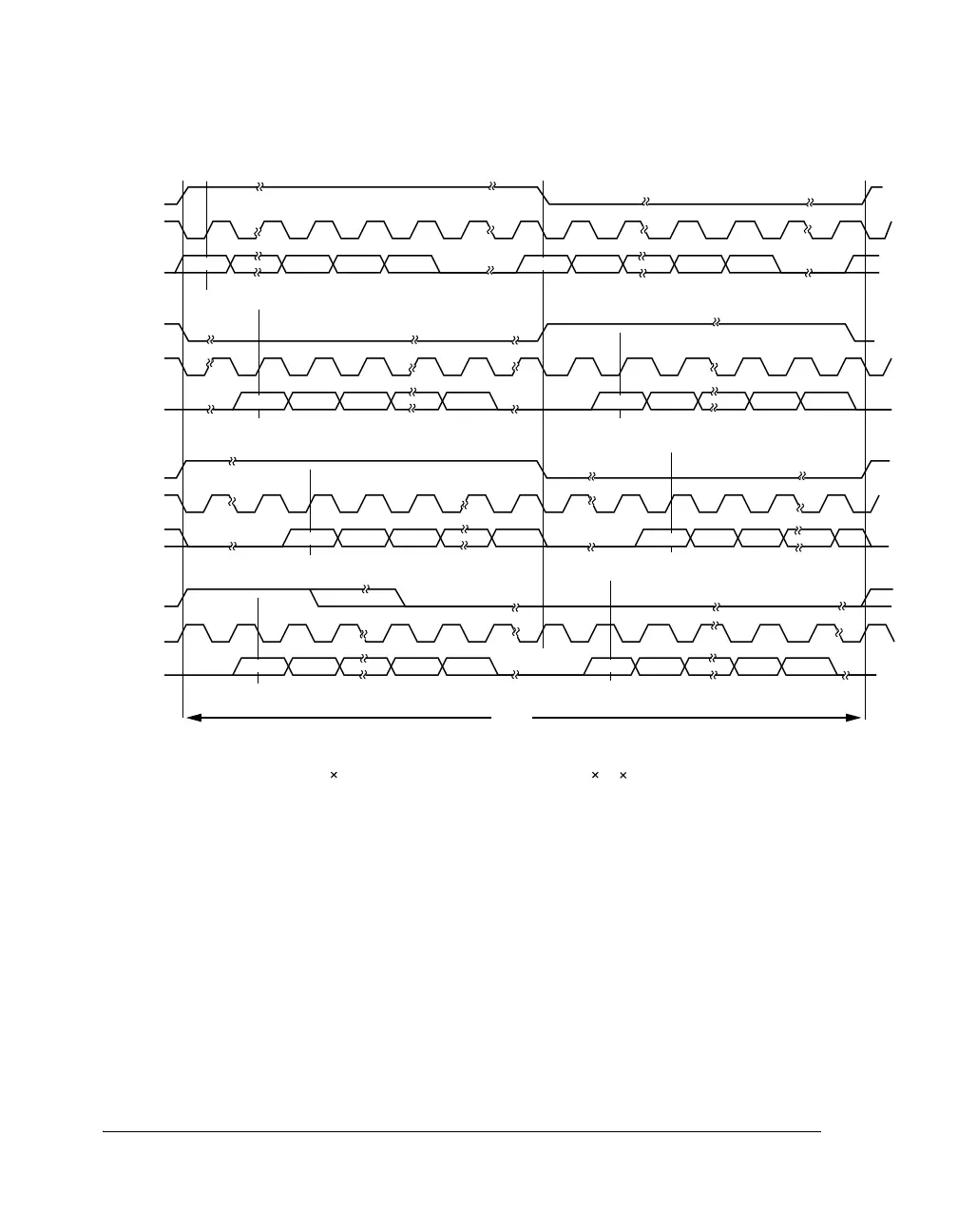

TDM MODE – 16 BITS TO 24 BITS PER CHANNEL

LEFT CHANNEL

RIGHT CHANNEL

LRCLK

SCLK

S DATA

LRCLK

SCLK

S DATA

LRCLK

SCLK

S DATA

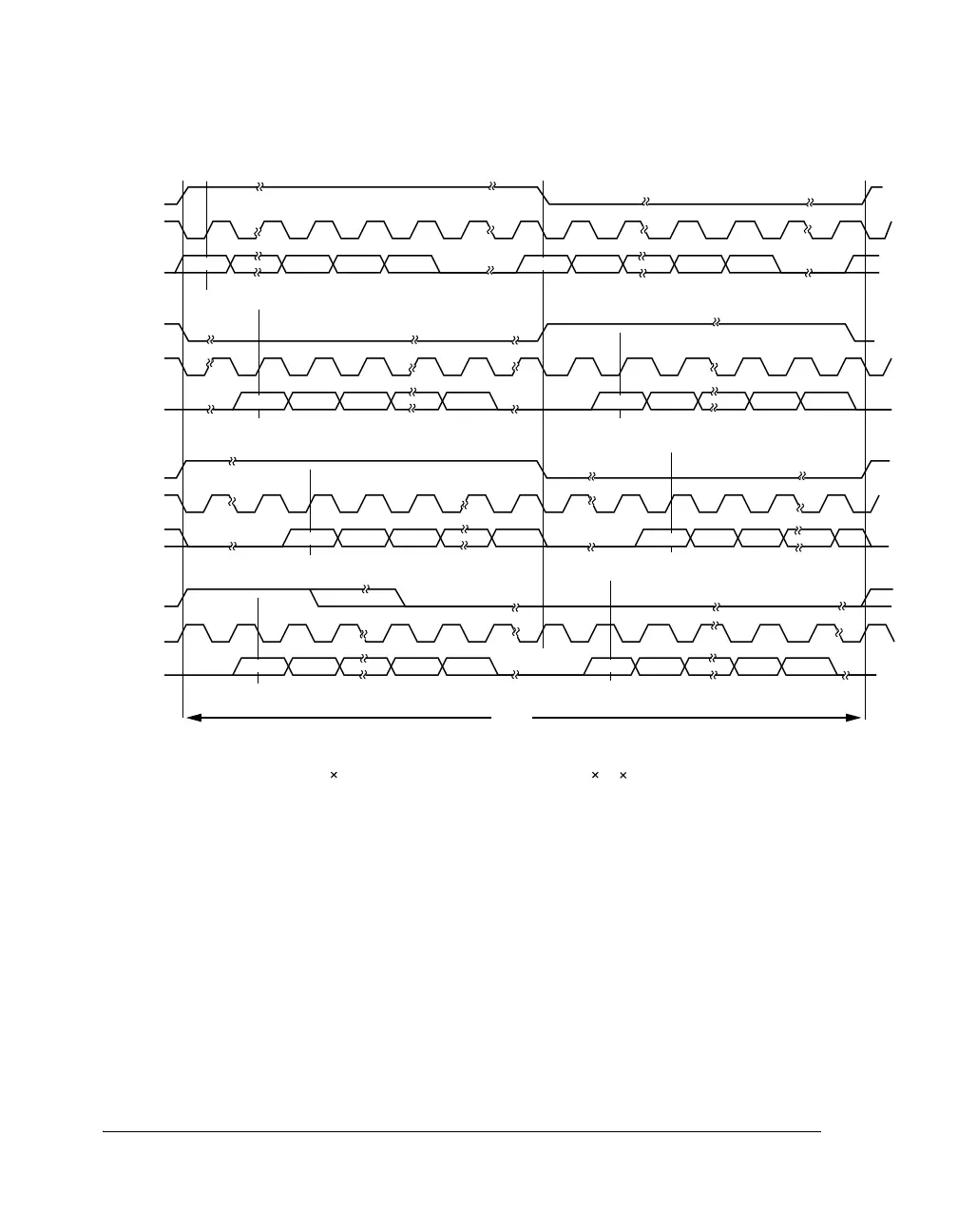

I2S MODE – 16 BITS TO 24 BITS PER CHANNEL

RIGHT-JUSTIFIED MODE – SELECT NUMBER OF BITS PER CHANNEL

LEFT-JUSTIFIED MODE – 16 BITS TO 24 BITS PER CHANNEL

NOTES

1

LRCLK NORMALLY OPERATES AT ASSOCIATIVE INPUT OR OUTPUT SAMPLE FREQUENCY (f

S

).

2

3

PLEASE NOTE THAT 8 BITS OF EACH 32-BIT SUBFRAME ARE USED FOR TRANSMITTING

MATCHED-PHASE MODE DATA.

SCLK FREQUENCY IS NORMALLY 64

LRCLK EXCEPT FOR TDM MODE WHICH IS N 64 fS,

WHERE N = NUMBER OF STEREO CHANNELS IN THE TDM CHAIN.

LSBLSB

LEFT CHANNEL

RIGHT CHANNEL

MSB LSB

LSB

MSB

MSB

MSB

MSB LSB

LSB

MSB

MSB LSB

LSB

MSB

LEFT CHANNEL

RIGHT CHANNEL

LRCLK

SCLK

S DATA

Loading...

Loading...