ADSP-214xx SHARC Processor Hardware Reference 15-13

Serial Peripheral Interface Ports

Transfer Initiate Mode

When the processor is enabled as a master, the initiation of a transfer is

defined by the TIMOD bits (1–0). Based on these two bits and the status of

the interface, a new transfer is started upon either a read of the RXSPIx reg-

isters or a write to the TXSPIx registers. This is summarized in Table 15-6.

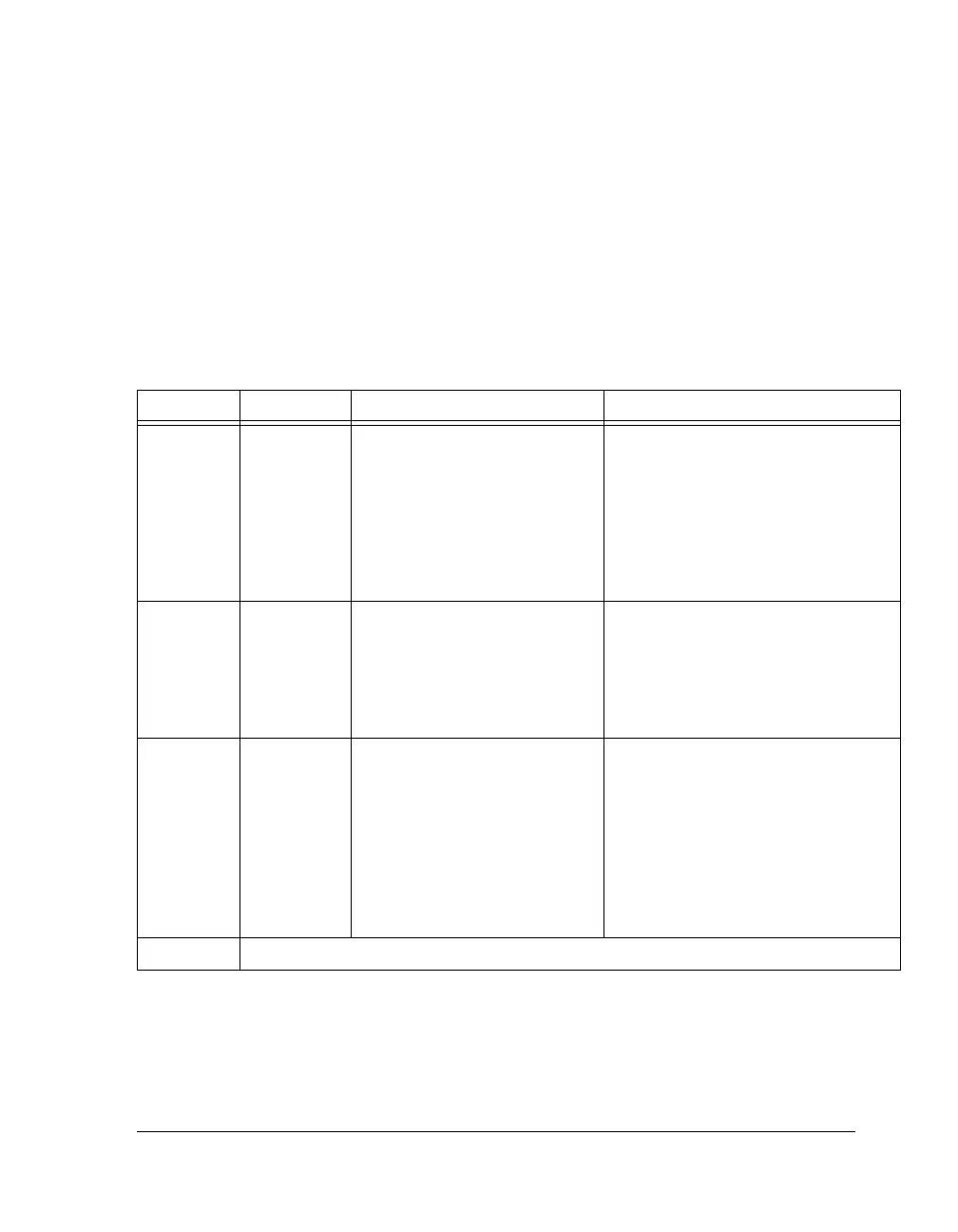

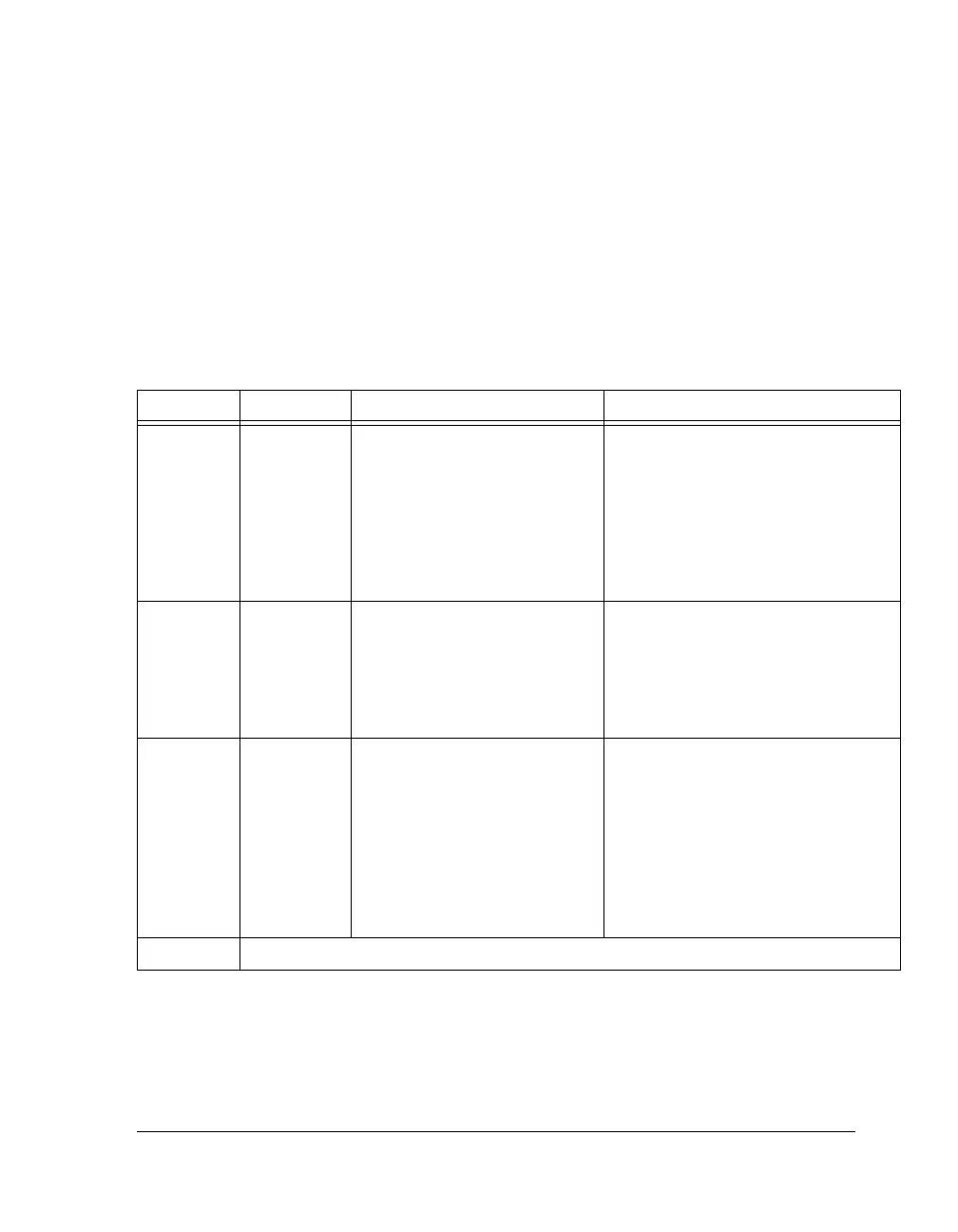

Table 15-6. Transfer Initiation

TIMOD Function Transfer Initiated Upon Action, Interrupt

00 Core Receive

and Transmit

Initiate new single word transfer

upon read of RXSPI and previous

transfer completed. The SPICLK

is generated after the data is read

from the buffer. In this configura-

tion, a dummy read is needed ini-

tially to receive all the data

transmitted from the transmitter.

The SPI interrupt is latched in every core

clock cycle in which the RXSPI buffer

has a word in it.

Emptying the RXSPI buffer or disabling

the SPI port at the same time (SPIEN =

0) stops the interrupt latch.

01 Core Transmit

and Receive

Initiate new single word transfer

upon write to TXSPI and previous

transfer completed.

The SPI interrupt is latched in every core

clock cycle in which the TXSPI buffer is

empty.

Writing to the TXSPI buffer or disabling

the SPI port at the same time (SPIEN =

0) stops the interrupt latch.

10 Transmit or

Receive with

DMA

Initiate new multiword transfer

upon write to DMA enable bit.

Individual word transfers begin

with either a DMA write to TXSPI

or a DMA read of RXSPI depend-

ing on the direction of the transfer

as specified by the SPIRCV bit.

If chaining is disabled, the SPI interrupt

is latched in the cycle when the DMA

count decrements from 1 to 0.

If chaining is enabled, interrupt function

is based on the PCI bit in the CP register.

If PCI = 0, the SPI interrupt is latched at

the end of the DMA sequence. If PCI =

1, then the SPI interrupt is latched after

each DMA in the sequence.

11 Reserved

Loading...

Loading...