Functional Description

21-10 ADSP-214xx SHARC Processor Hardware Reference

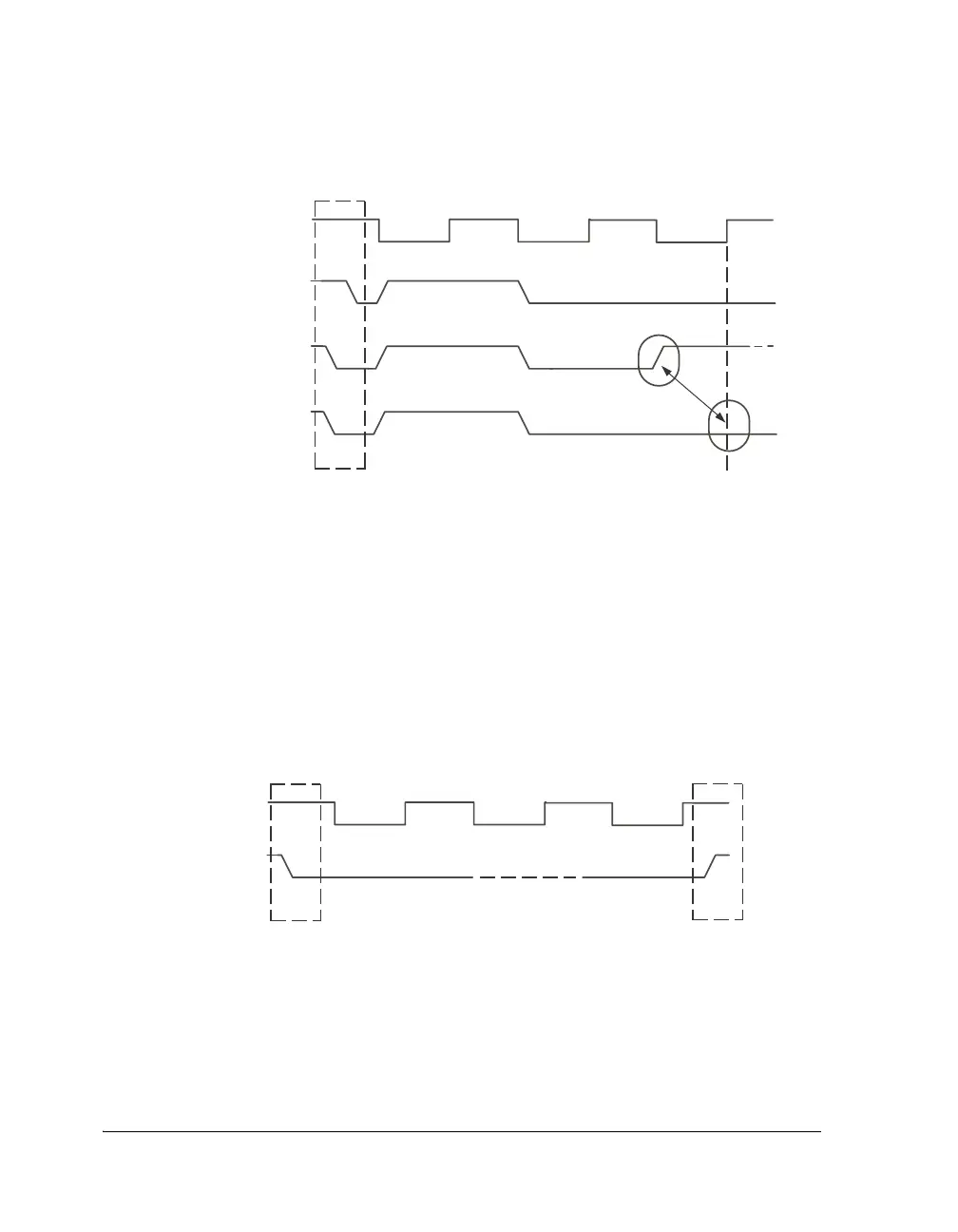

Start and Stop Conditions

Start and stop conditions involve serial data transitions while the serial

clock is at logic 1 level. The TWI controller generates and recognizes these

transitions. Typically, start and stop conditions occur at the beginning

and at the conclusion of a transmission, with the exception of repeated

start “combined” transfers, as shown in Figure 21-6.

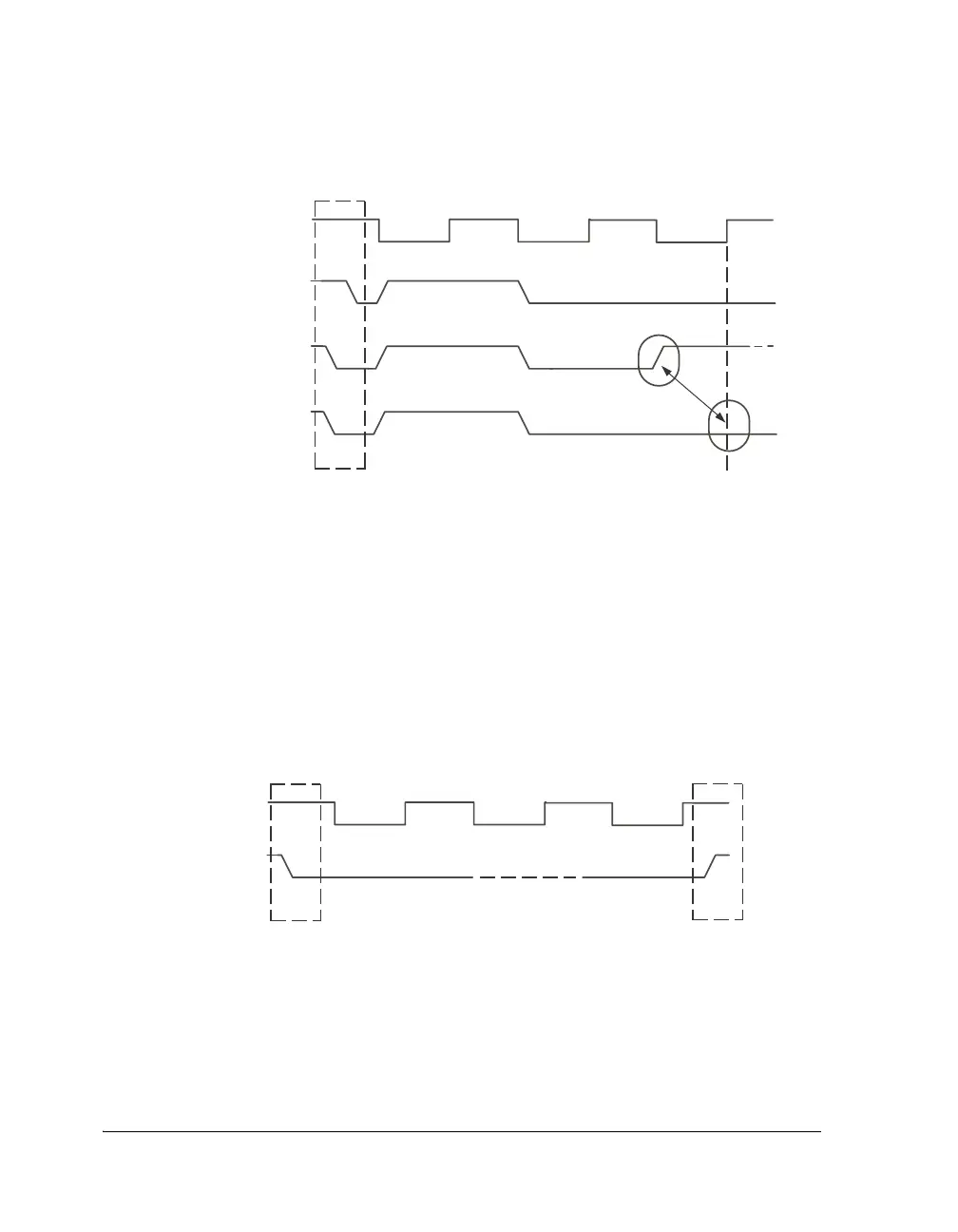

Figure 21-5. TWI Bus Arbitration

Figure 21-6. TWI Start and Stop Conditions

START

TWI_CLOCK (BUS)

TWI CONTROLLER

DATA

SECOND MASTER

DATA

TWI_DATA (BUS)

ARBITRATION

LOST

START

TWI_CLOCK (BUS)

TWI_DATA (BUS)

STOP

Loading...

Loading...