ADSP-214xx SHARC Processor Hardware Reference 3-111

External Port

Delay Line DMA

Delay line DMA is used to support reads and writes to external delay line

buffers with limited core interaction. In this sense, delay line DMA is basi-

cally a quantity of integrated writes followed by reads from external

memory-called a delay line DMA access. Delay line DMA is described in

the following sections.

The delay line DMA access consists of the following accesses in the order

listed and is shown in Figure 3-28 on page 3-113. Note that in the figure

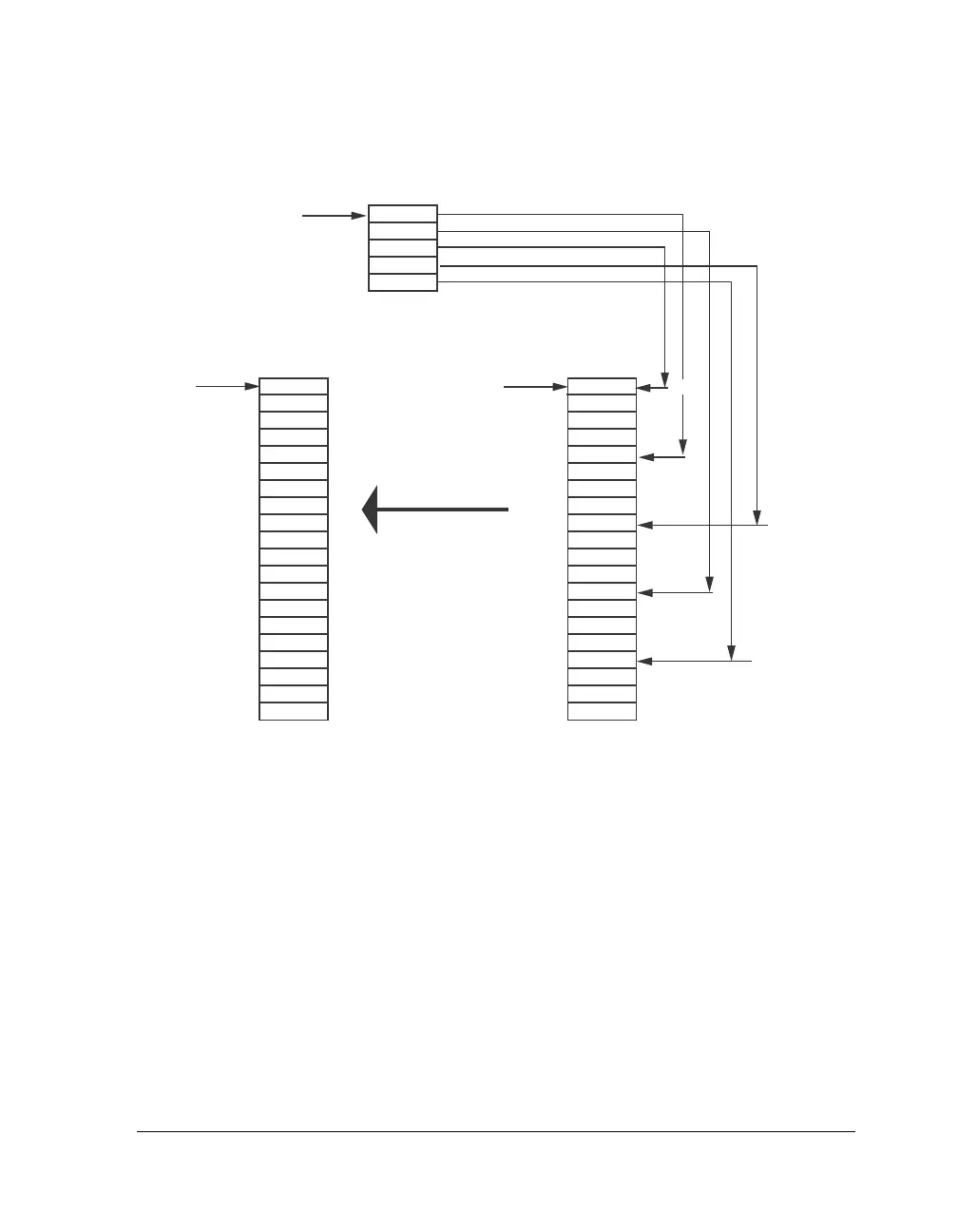

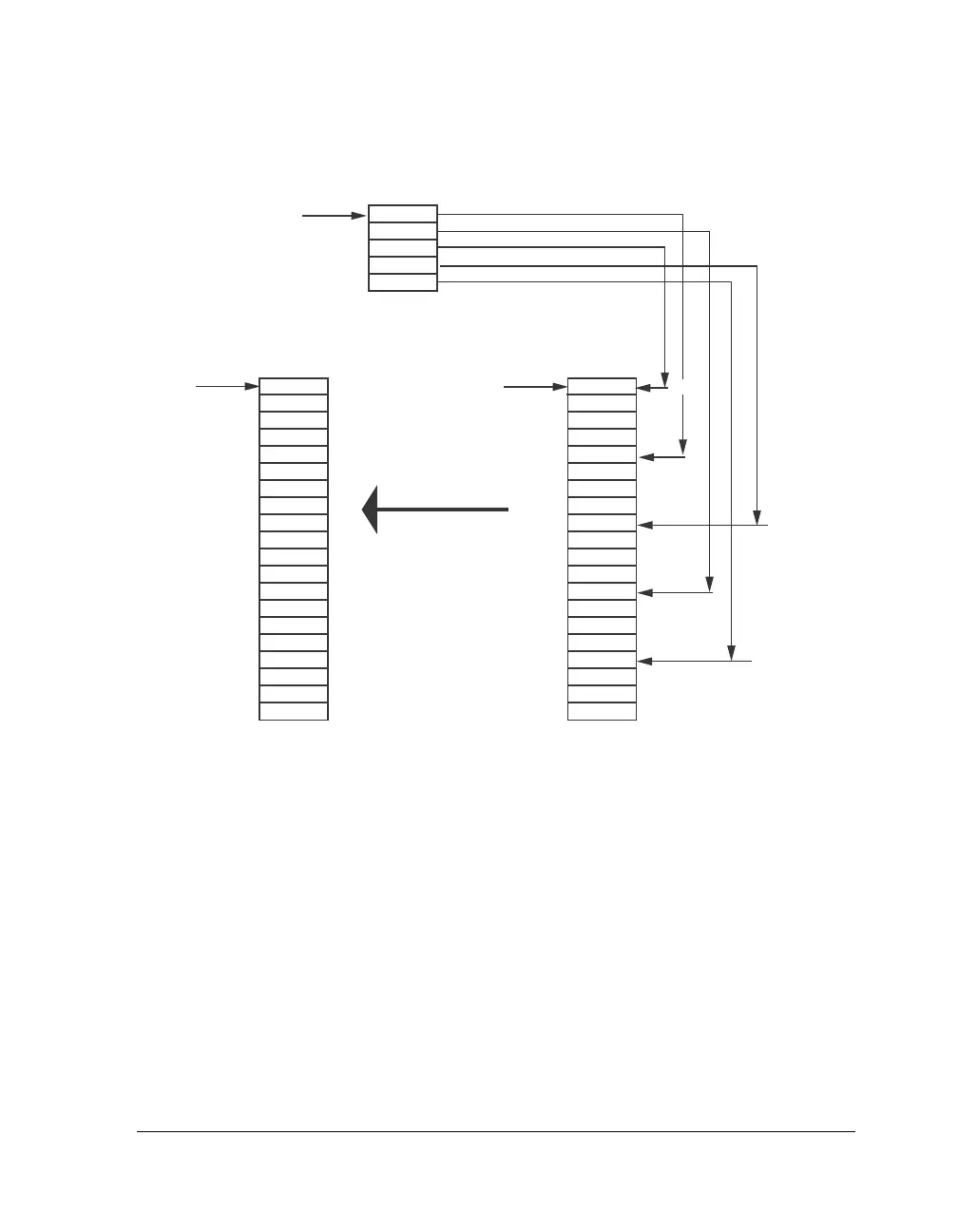

Figure 3-27. Circular Gather DMA (Reads)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

DESTINATION

INDEX (IIEP)

SOURCE INDEX (EIEP)

SOURCE BASE (EBEP)

DESTINATION BUFFER

SOURCE BUFFER

TAP LIST BUFFER

4

12

20

28

36

EIEP + 36

EIEP + 28

EIEP + 12

EIEP + 4

EIEP + 20

TAP LIST POINTER (TPEP)

Loading...

Loading...