ADSP-214xx SHARC Processor Hardware Reference 10-25

Serial Ports

Standard Serial Mode

The standard serial mode lets programs configure serial ports for use by a

variety of serial devices such as serial data converters and audio codecs. In

order to connect to these devices, a variety of clocking, framing, and data

formatting options are available.

Timing Control Bits

Several bits in the SPCTLx register enable and configure standard serial

mode operation:

• Internal Clock (ICLK)

• Internal Frame Sync (IFS)

• Frame Sync Required (FSR)

• Sampling Edges Frame Sync/data (CKRE)

• Logic Level Frame Sync (

LFS)

• Late Frame Sync (LAFS)

• Word length (

SLEN, 3–32 bits)

• Word Order (

LSBF)

• Word Packing (

PACK)

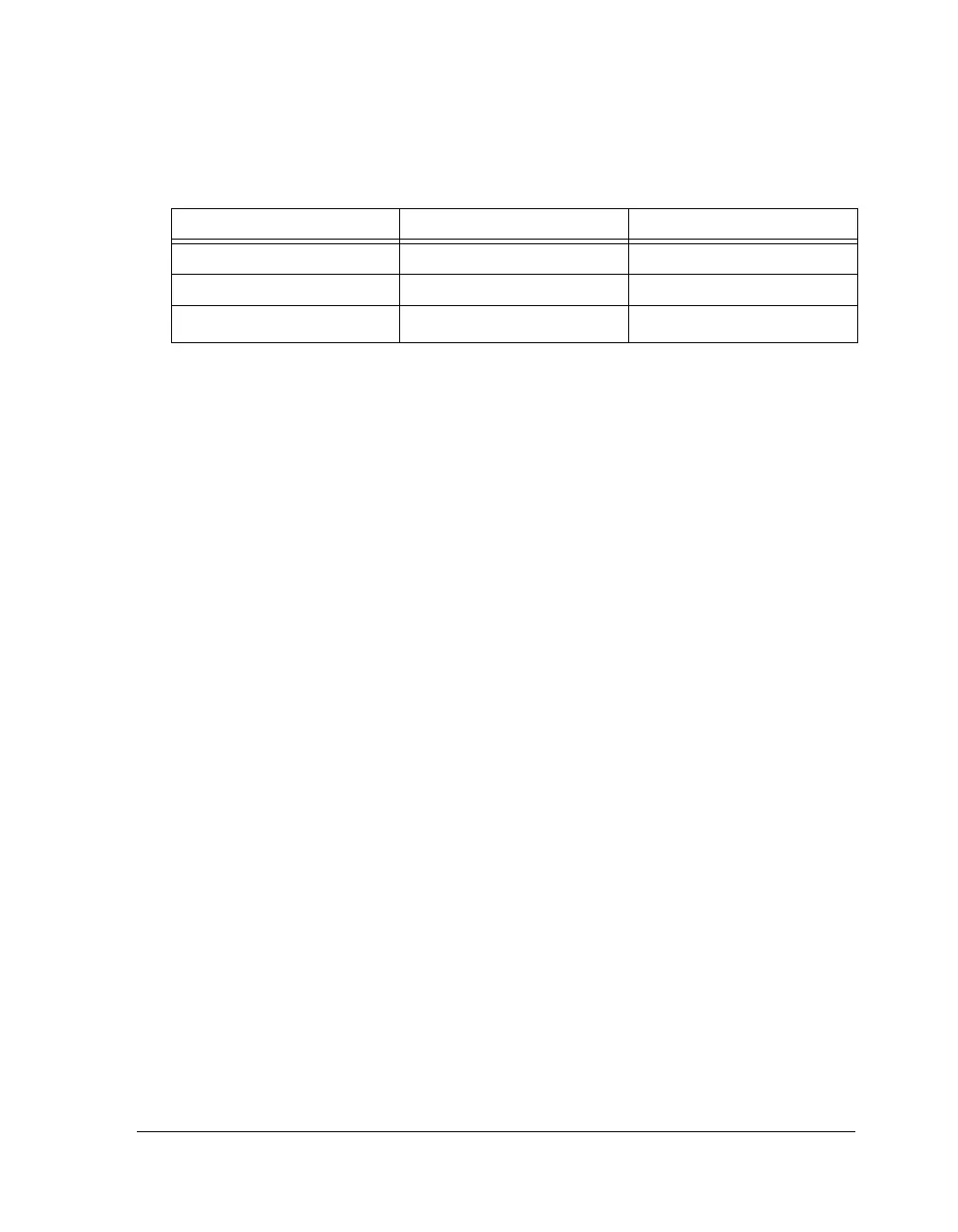

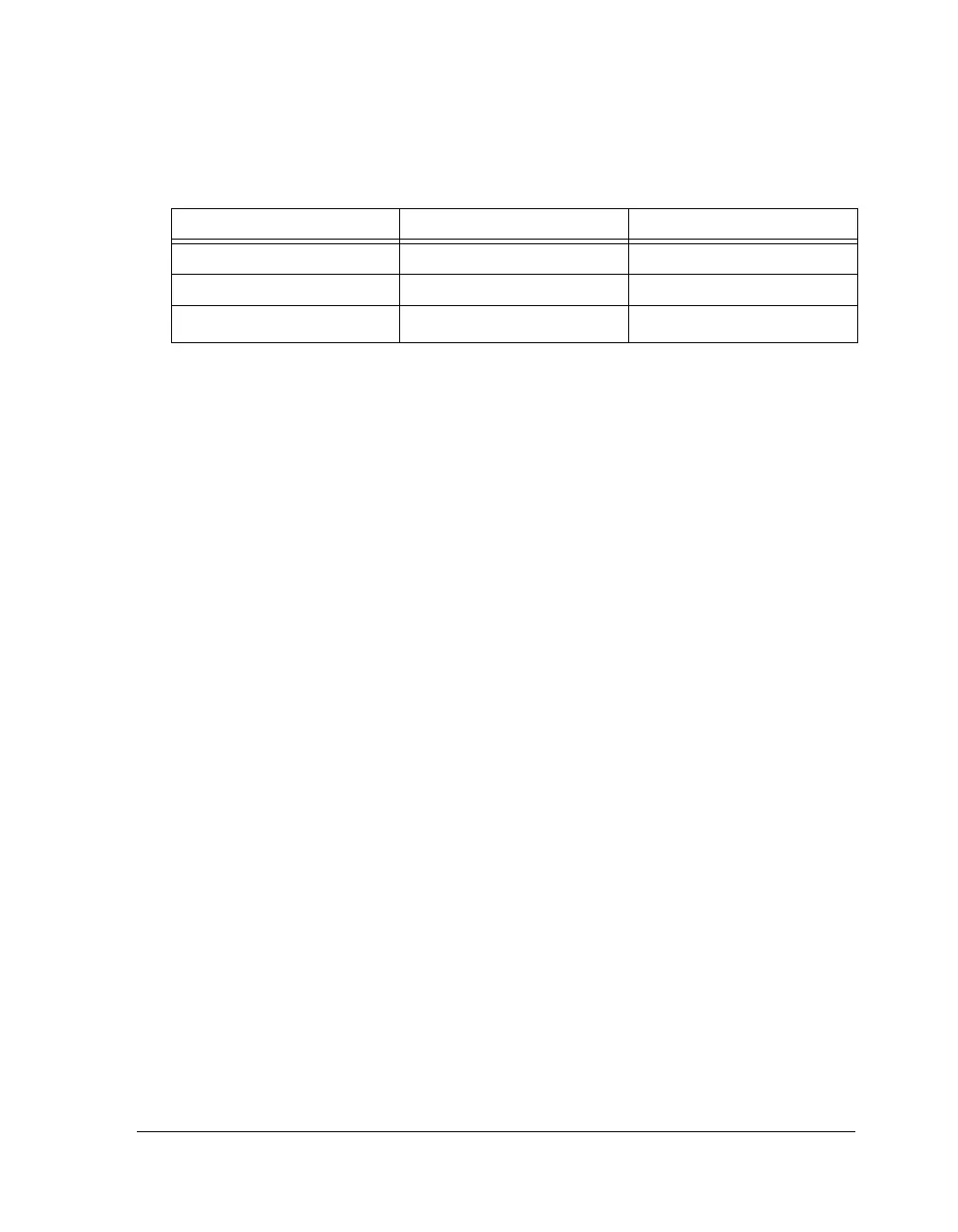

Table 10-8. Channel Order First

OPMODE L_FIRST = 0 L_FIRST = 1

Left-Justified Data first after rising edge Data first after falling edge

Packed Data first after rising edge Data first after falling edge

I

2

S

Data first after falling edge Data first after rising edge

Loading...

Loading...