DMA Channel Registers

2-10 ADSP-214xx SHARC Processor Hardware Reference

Data Buffers

The data buffers or FIFOs (shown in Table 2-9) are used by each DMA

channel to store data during the priority arbitration time period. The buf-

fers (depending on the peripheral) are accessed by both DMA and the

core. Note that all transmit buffers are write-only-to-clear (WOC) and all

receive buffers are read-only-to-clear (ROC).

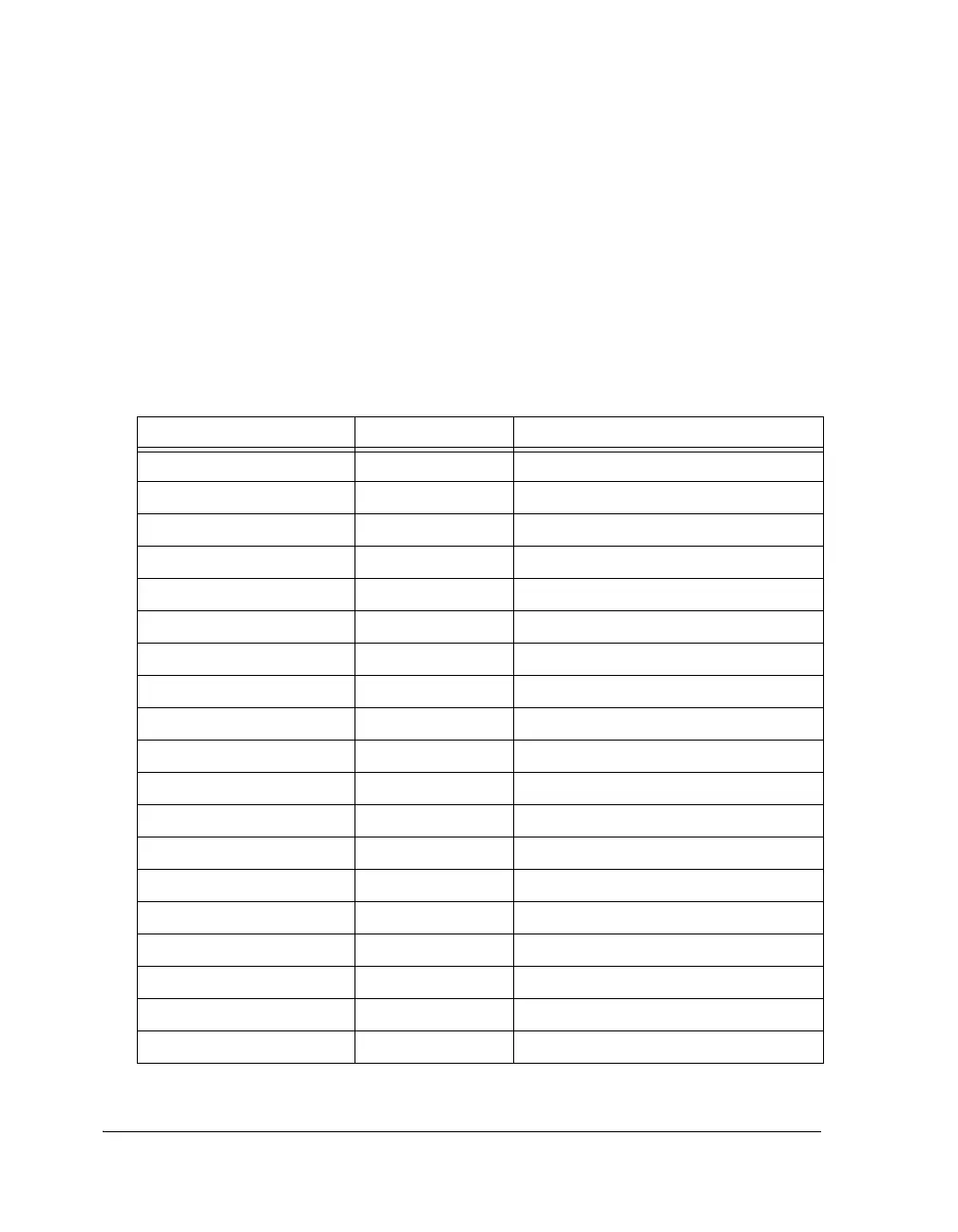

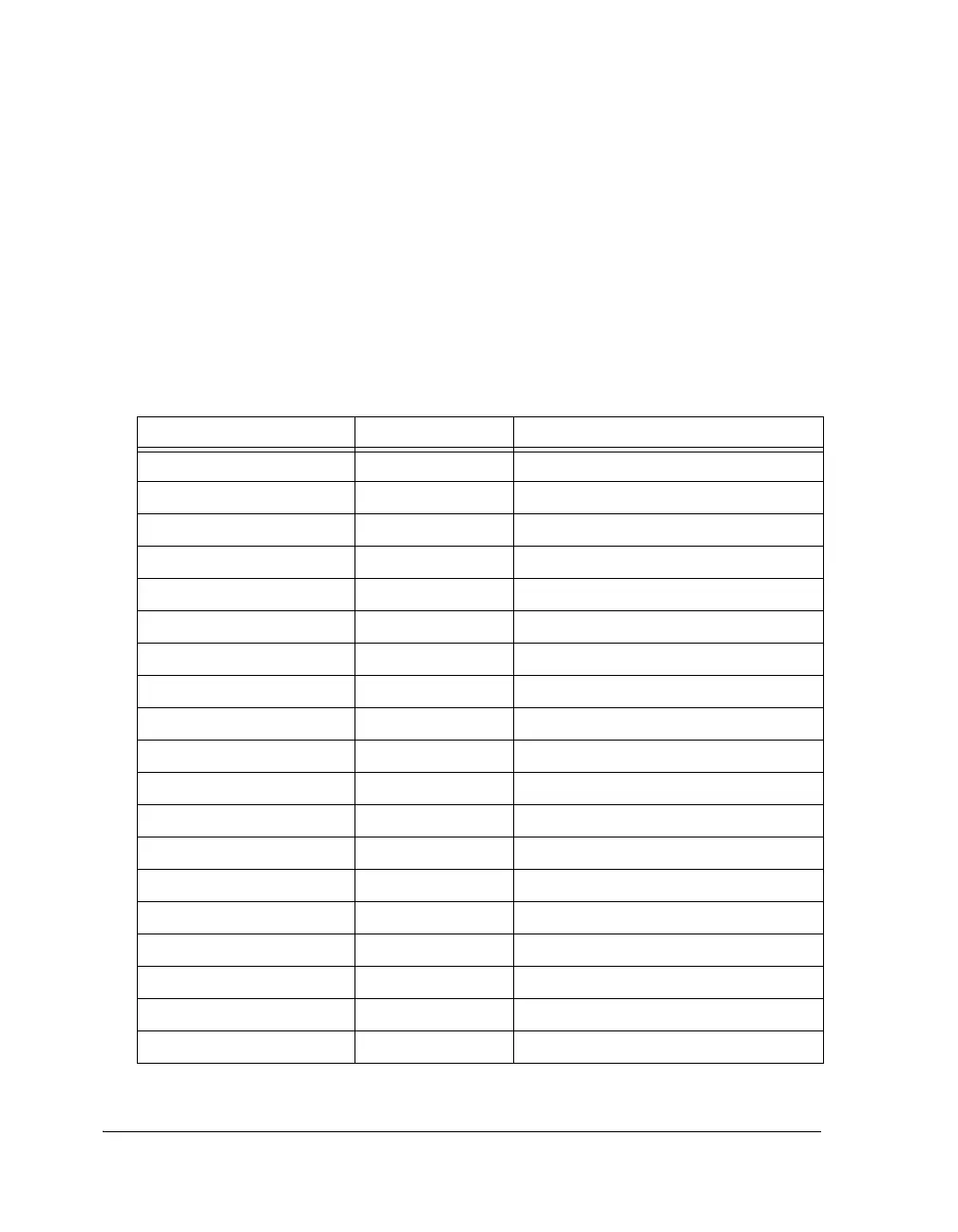

Table 2-9. Data Buffers

Buffer Name FIFO Depth Description

TXSP0–7A 2 SPORTA Transmit

TXSP0–7B 2 SPORTB Transmit

RXSP0–7A 2 SPORTA Receive

RXSP0–7B 2 SPORTB Receive

TXSPI 2 SPI Transmit

TXSPIB 2 SPIB Transmit

RXSPI 2 SPI Receive

RXSPIB 2 SPIB Receive

RXSPI_SHADOW 2 SPI Receive Shadow (RO)

RXSPIB_SHADOW 2 SPIB Receive Shadow (RO)

SPI DMA 4 DMA only

SPIB DMA 4 DMA only

IDP_FIFO 8 IDP FIFO Receive

TXLB0–1 2 Link Port Transmit Buffer

TXLB0–1_IN_SHADOW 1 Link Port Transmit Shadow Buffer (RO)

TXLB0–1_OUT_SHADOW 1 Link Port Transmit Shadow Buffer (RO)

RXLB0–1 2 Link Port Receive Buffer

RXLB0–1_IN_SHADOW 1 Link Port Receive Shadow Buffer (RO)

RXLB0–1_OUT_SHADOW 1 Link Port Receive Shadow Buffer (RO)

Loading...

Loading...