SRU Programming

15-4 ADSP-214xx SHARC Processor Hardware Reference

SRU Programming

Both SPI and SPIB signals are available through the SRU2, and are routed

as described in Table 15-3.

Since the SPI supports a gated clock, it is recommended that programs

enable the SPI clock output signal with its related pin buffer enable. This

can be done using the macro SRU (SPI_CLK_PBEN_O, PBEN_03_I). If these

signals are routed statically high as in SRU (high, PBEN_03_I) some SPI

timing modes that are based on polarity and phase may not work correctly

because the timing is violated.

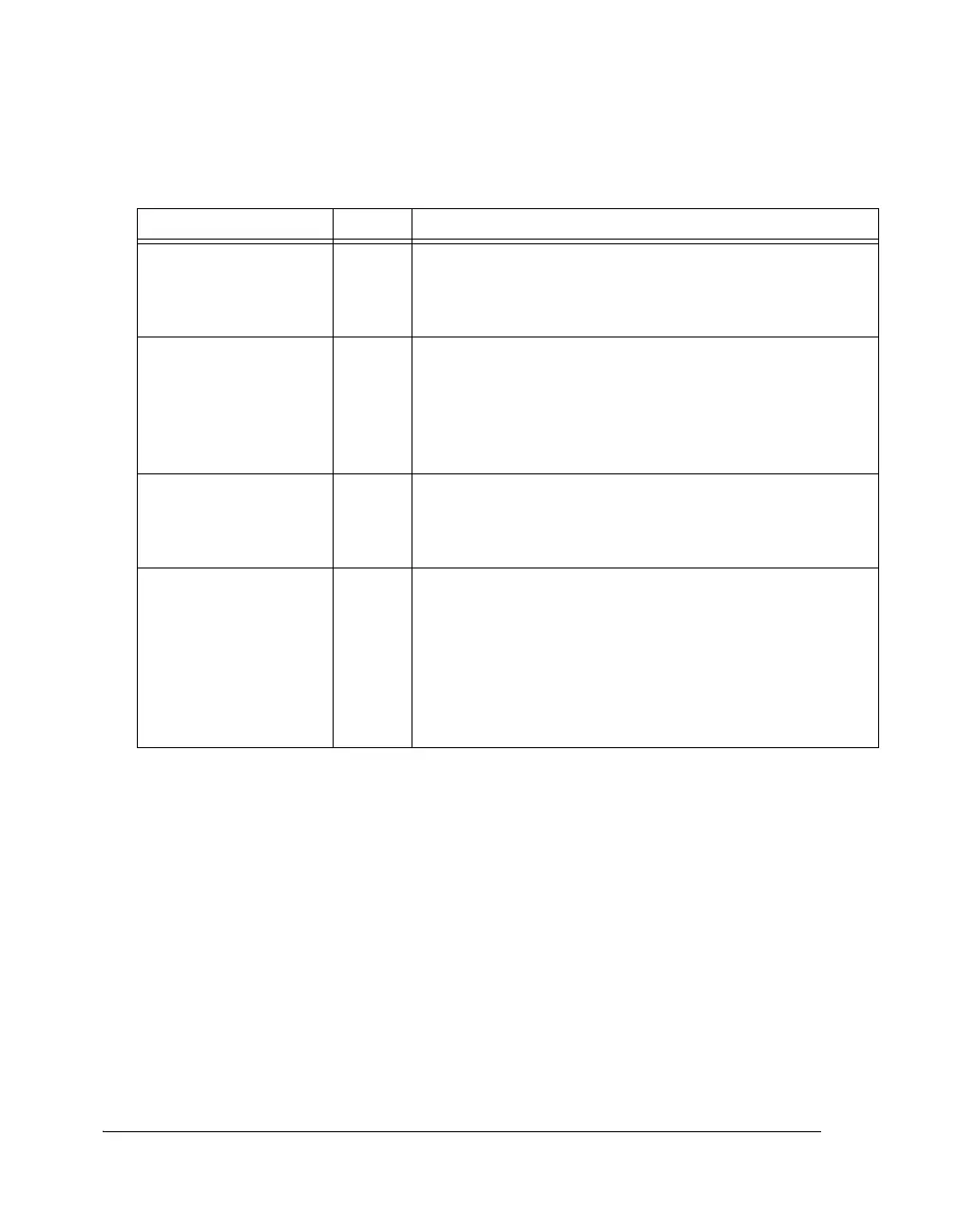

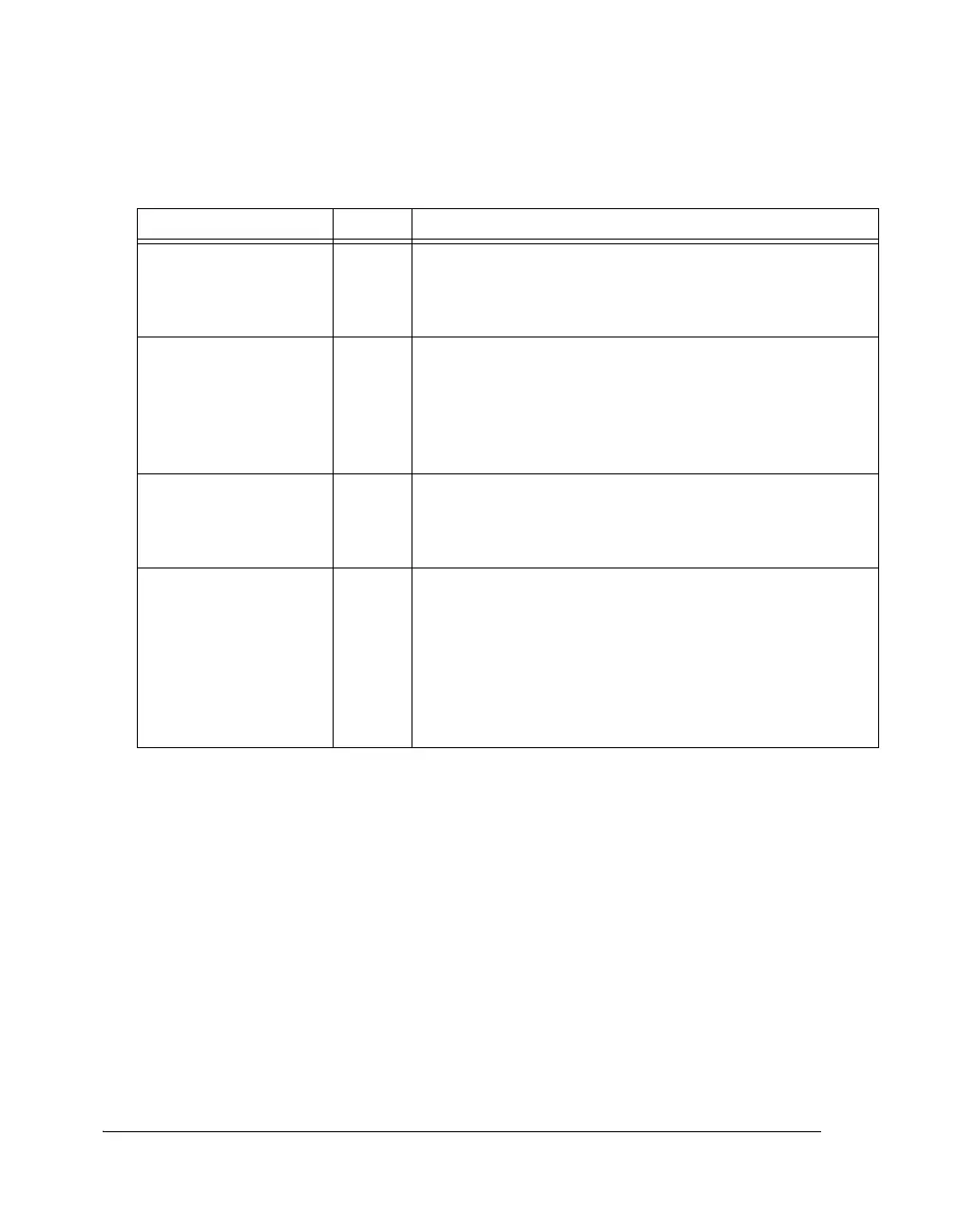

SPI_MOSI_I/O

SPIB_MOSI_I/O

I/O SPI Master Out Slave In. This data line transmits the output data

from the master device and receives the input data to a slave

device. This data is shifted out from the MOSI pin of the master

and shifted into the MOSI input(s) of the slave(s).

SPI_MISO_I/O

SPIB_MISO_I/O

I/O SPI Master In Slave Out. This data line transmits the output data

from the slave device and receives the input data to the master

device. This data is shifted out from the MISO pin of the slave

and shifted into the MISO input of the master. There may be no

more than one slave that is transmitting data during any particular

transfer.

SPI_FLG3-0_O

SPIB_FLG3-0_O

O SPI Slave Select Out. The slave select pins are used to address up

to 4 slaves in a multi device system. This functionality can be

routed to any of the DPI pins. This frees up the multiplexed core

flags for other purposes.

SPI_CLK_PBEN_O

SPIB_CLK_PBEN_O

SPI_MOSI_PBEN_O

SPIB_MOSI_PBEN_O

SPI_MISO_PBEN_O

SPIB_MISO_PBEN_O

SPI_FLG3-0_PBEN_O

SPIB_FLG3-0_PBEN_O

O SPI Pin buffer Enable Out Signal. Only driven in master mode.

The SPIx_FLGx_PBEN_O signals are enabled if the correspond-

ing DSxEN bits in the SPIFLAG register are set.

Table 15-2. SPI Pin Descriptions (Cont’d)

Internal Node Type Description

Loading...

Loading...