ADSP-214xx SHARC Processor Hardware Reference 2-13

I/O Processor

Bit 19 of the chain pointer register is the program controlled interrupt

(

PCI) bit. This bit controls whether an interrupt is latched after every

DMA in the chain (when set = 1), or whether the interrupt is latched after

the entire DMA sequence completes (if cleared = 0). If a program contains

a single chained DMA then the PCI interrupt is generated coincident with

the start of next TCB loading.

However, if running multiple DMA channels this coincidence is no longer

true since there are different DMA channel priorities versus interrupt

priorities.

The PCI bit only effects DMA channels that have chaining enabled.

Also, interrupt requests enabled by the PCI bit are maskable with

the IMASK register.

TCB Storage

This section lists all the different TCB memory allocations used for DMA

chaining on the peripherals. Note that all TCBs must be located in inter-

nal memory except SPORTs, where TCBs can exist in external memory.

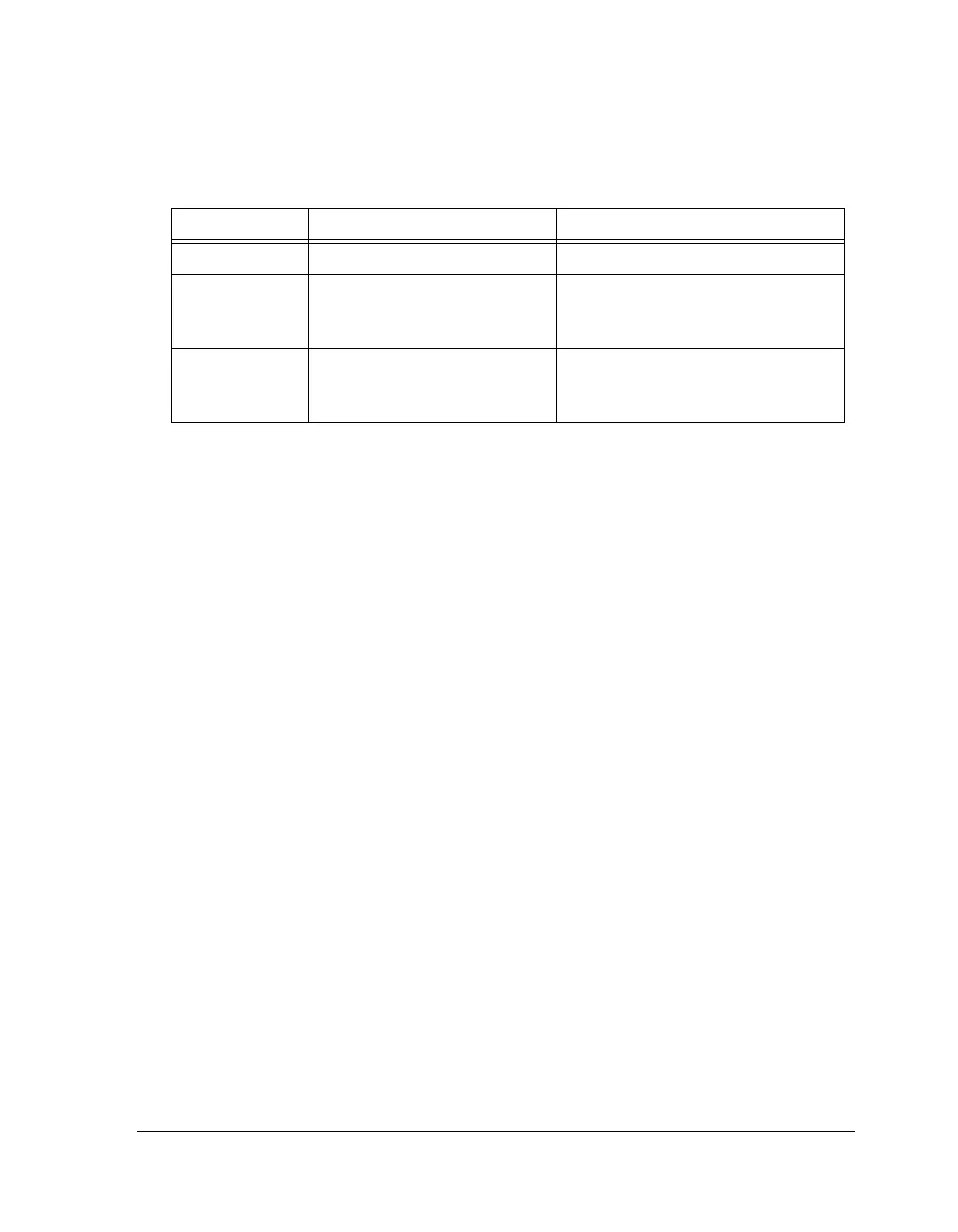

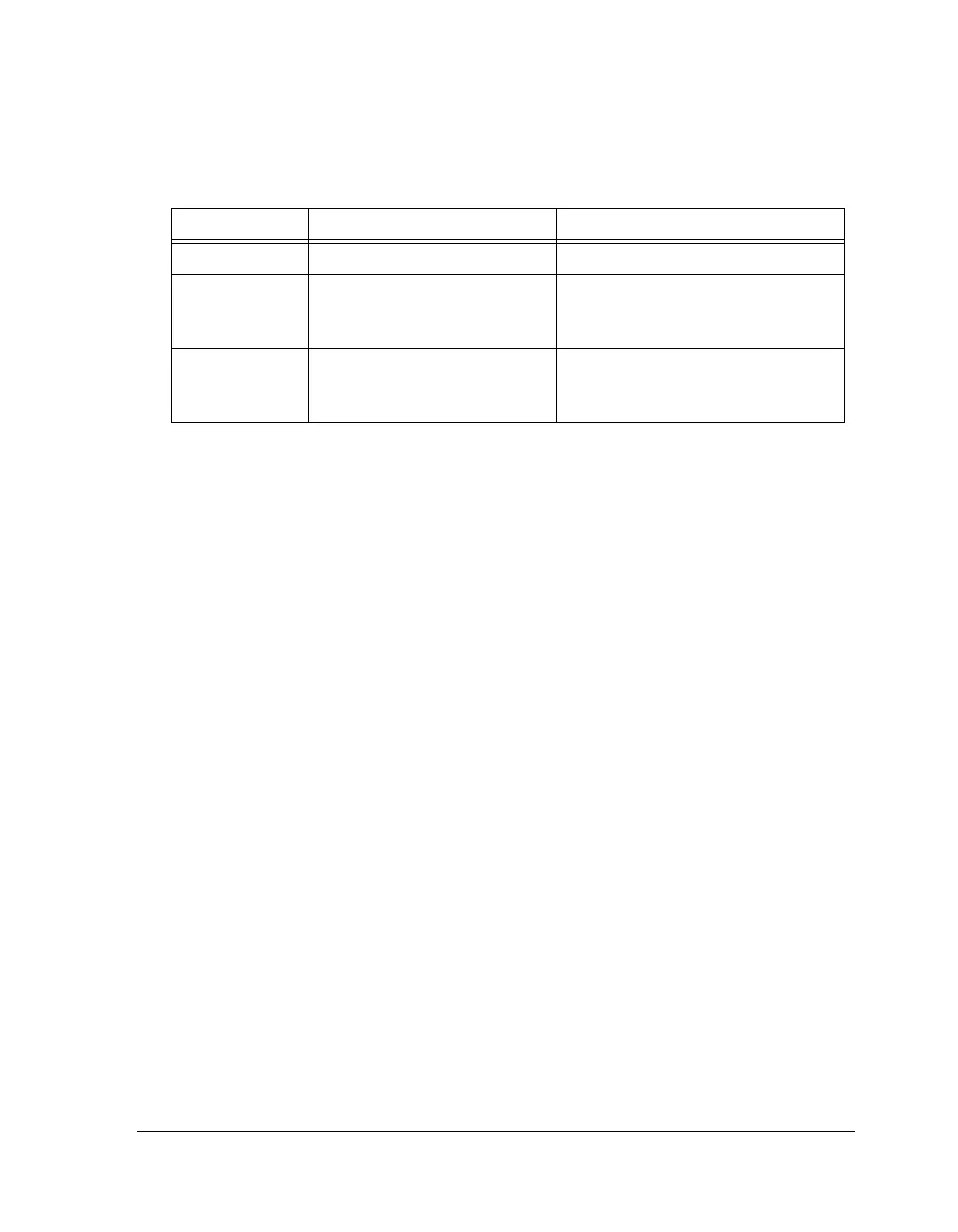

Table 2-13. FFT Input Chain Pointer Register (CPIFFT)

Bit Name Description

18–0 IIx address Next chain pointer address

19 PCI Program controlled interrupt

0 = no interrupt after current TCB

1 = interrupt after current TCB

20 COEFFSEL Coefficient select for next TCB

0 = next TCB is data TCB

1 = next TCB is coeff TCB

Loading...

Loading...