Peripherals Routed Through the DPI

A-252 ADSP-214xx SHARC Processor Hardware Reference

DMA Status Registers (UART0TXSTAT,

UART0RXSTAT)

These read-only registers (described in Table A-134 and Table A-135)

provide DMA status information.

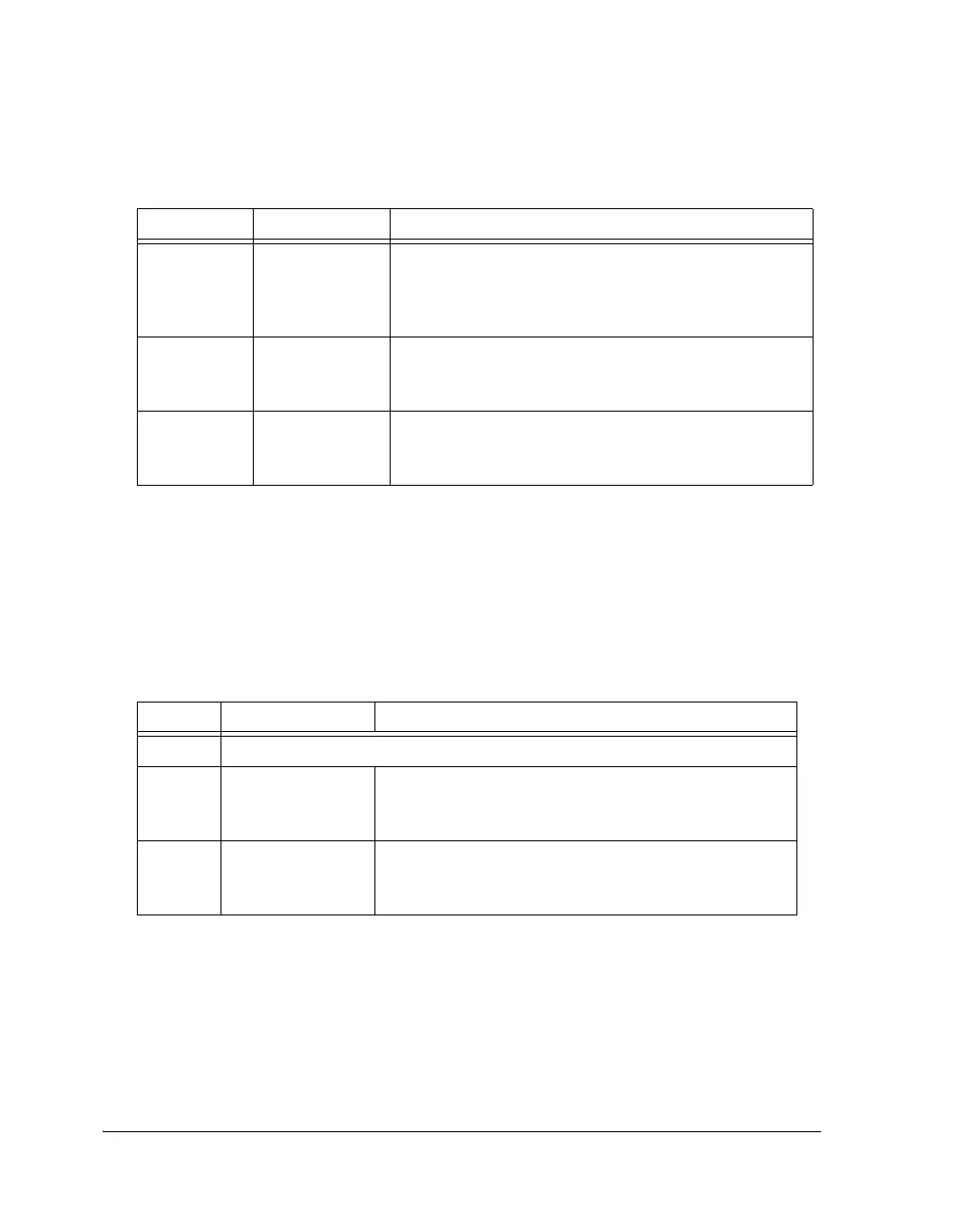

Table A-133. UART0RXCTL Register Descriptions (RW)

Bit Name Description

0UARTENReceive Buffer Enable.

0 = Clears the receive buffer

1 = Enables the receive buffer (this bit needs to be enabled

regardless of core or DMA access)

1 UARTDEN DMA Enable.

0 = Disables DMA

1 = Enables DMA on the specified channel

2 UARTCHEN Chain Pointer DMA Enable.

0 = Disable chained DMA

1 = Enable chained DMA on the specified channel

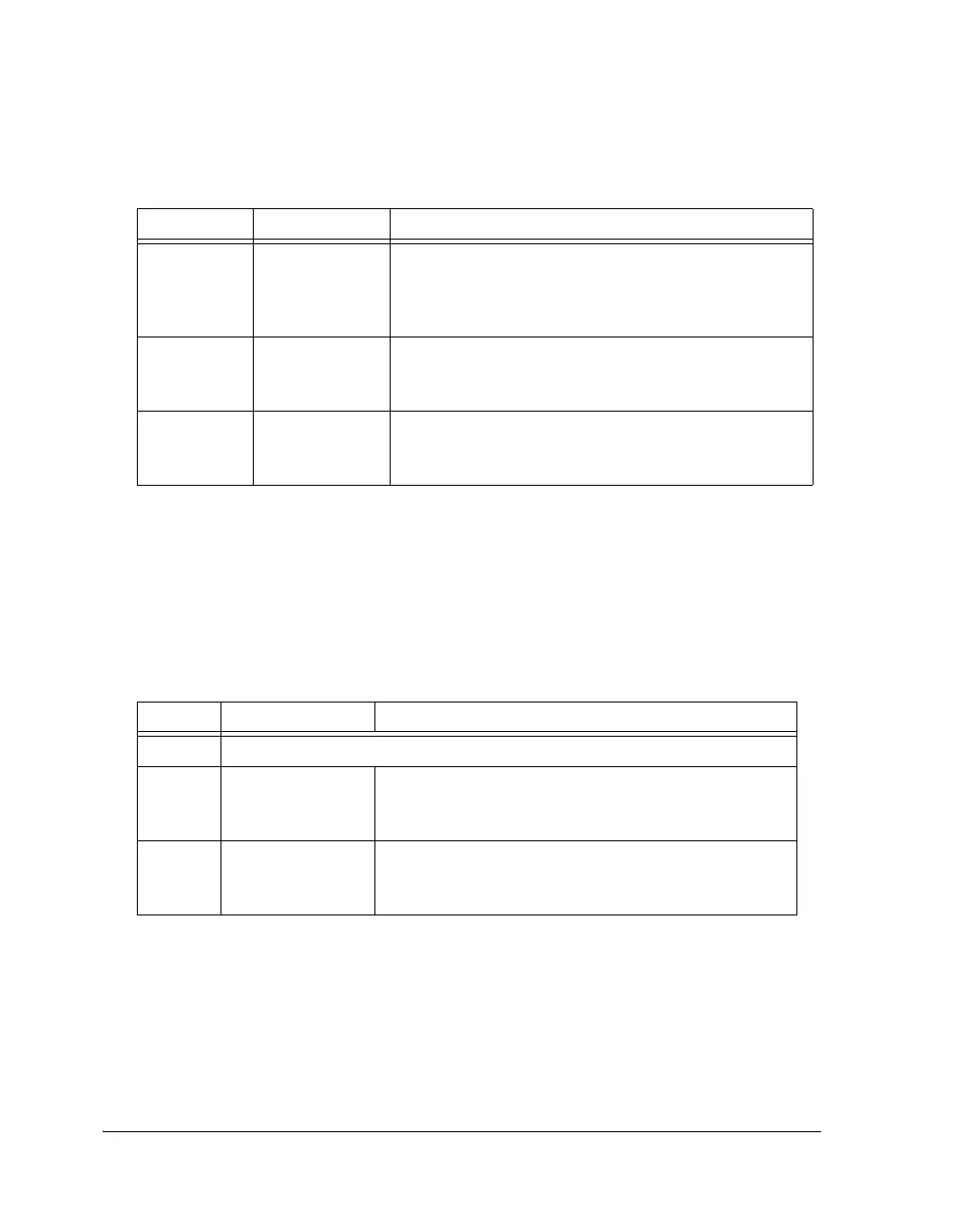

Table A-134. UART0TXSTAT Register Bit Descriptions (RO)

Bit Name Description

0 Reserved

1 UARTDMASTAT DMA Status. Provides DMA status.

0 = TX DMA is inactive

1 = TX DMA is active

2 UARTCHSTAT DMA Chaining Status. Provides DMA chaining status.

0 = TX DMA chain loading is inactive

1 = TX DMA chain loading is active

Loading...

Loading...