ADSP-214xx SHARC Processor Hardware Reference A-71

Registers Reference

Status Registers (PWMSTATx)

These 16-bit registers, described in Table A-38, report the status of the

phase and mode for each PWM group.

Output Disable Registers (PWMSEGx)

These 16-bit registers, described in Table A-39, control the output signals

of the four PWM groups. The output signals are enabled by default.

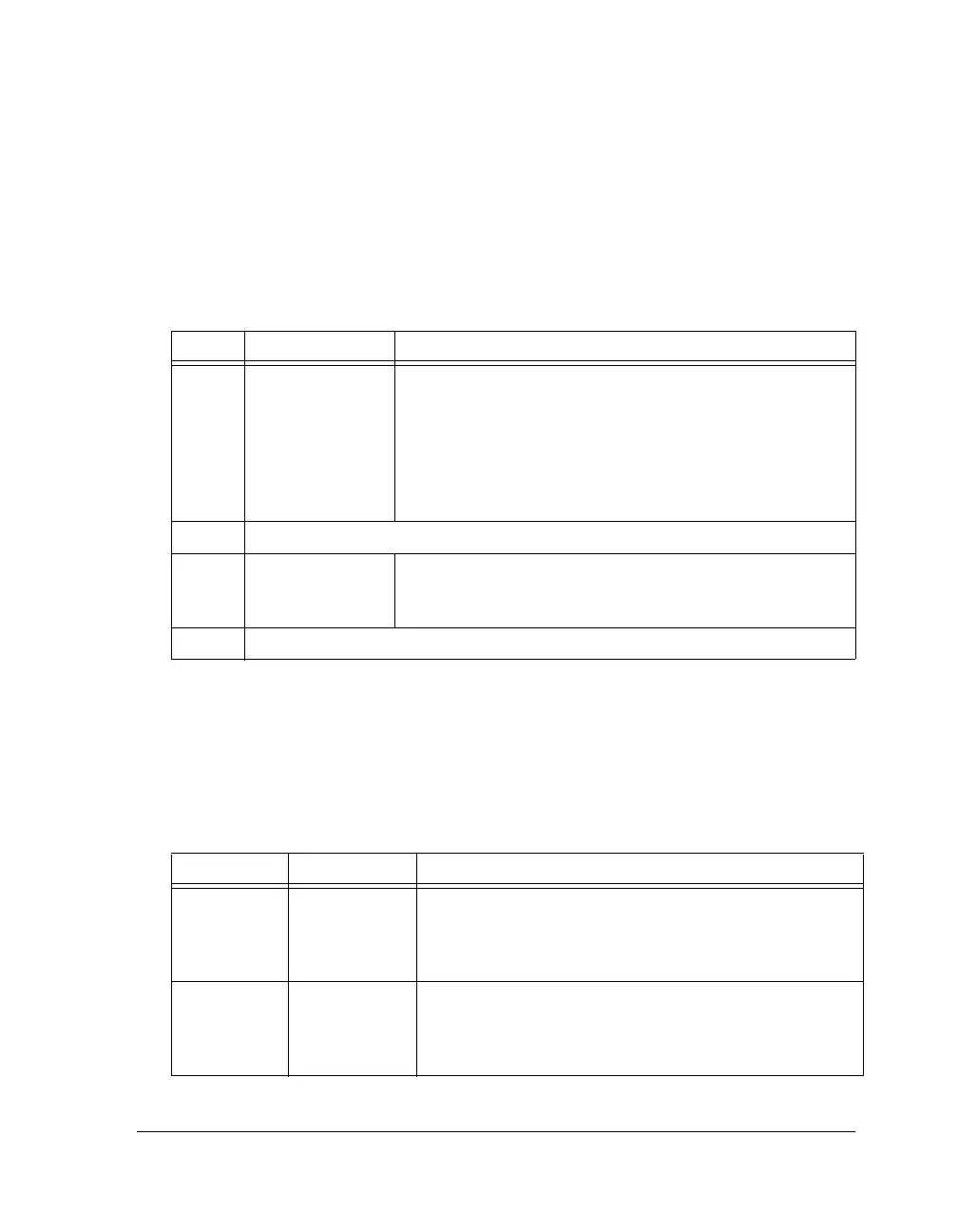

Table A-38. PWMSTATx Register Bit Descriptions (RO)

Bit Name Description

0 PWM_PHASE PWM Phase Status. Set during center aligned mode in the sec-

ond half of each PWM period. Allows programs to determine the

particular half-cycle (first or second) during PWM interrupt ser-

vice routine, if required.

0 = First half

1 = Second half (default)

In edge aligned mode this bit is always set.

1 Reserved

2 PWM_PAIRSTAT PWM Paired Mode Status.

0 = Inactive paired mode

1 = Active paired mode

15–3 Reserved

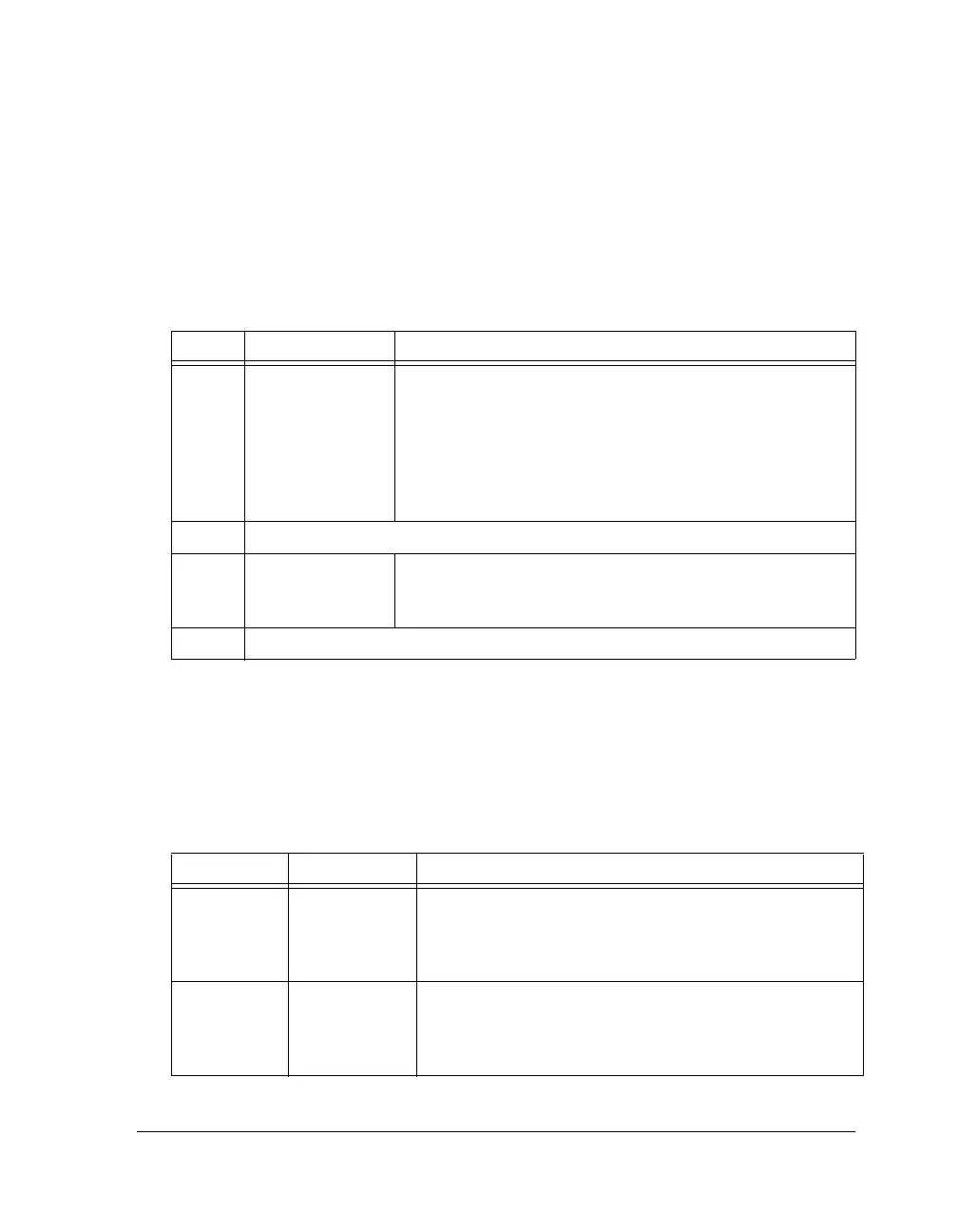

Table A-39. PWMSEGx Register Bit Descriptions (RW)

Bit Name Description

0PWM_BHChannel B High Disable. Enables or disables the channel B

output signal.

0 = Enable

1 = Disable

1PWM_BLChannel B Low Disable. Enables or disables the channel B

output signal.

0 = Enable

1 = Disable

Loading...

Loading...