Interrupts

2-46 ADSP-214xx SHARC Processor Hardware Reference

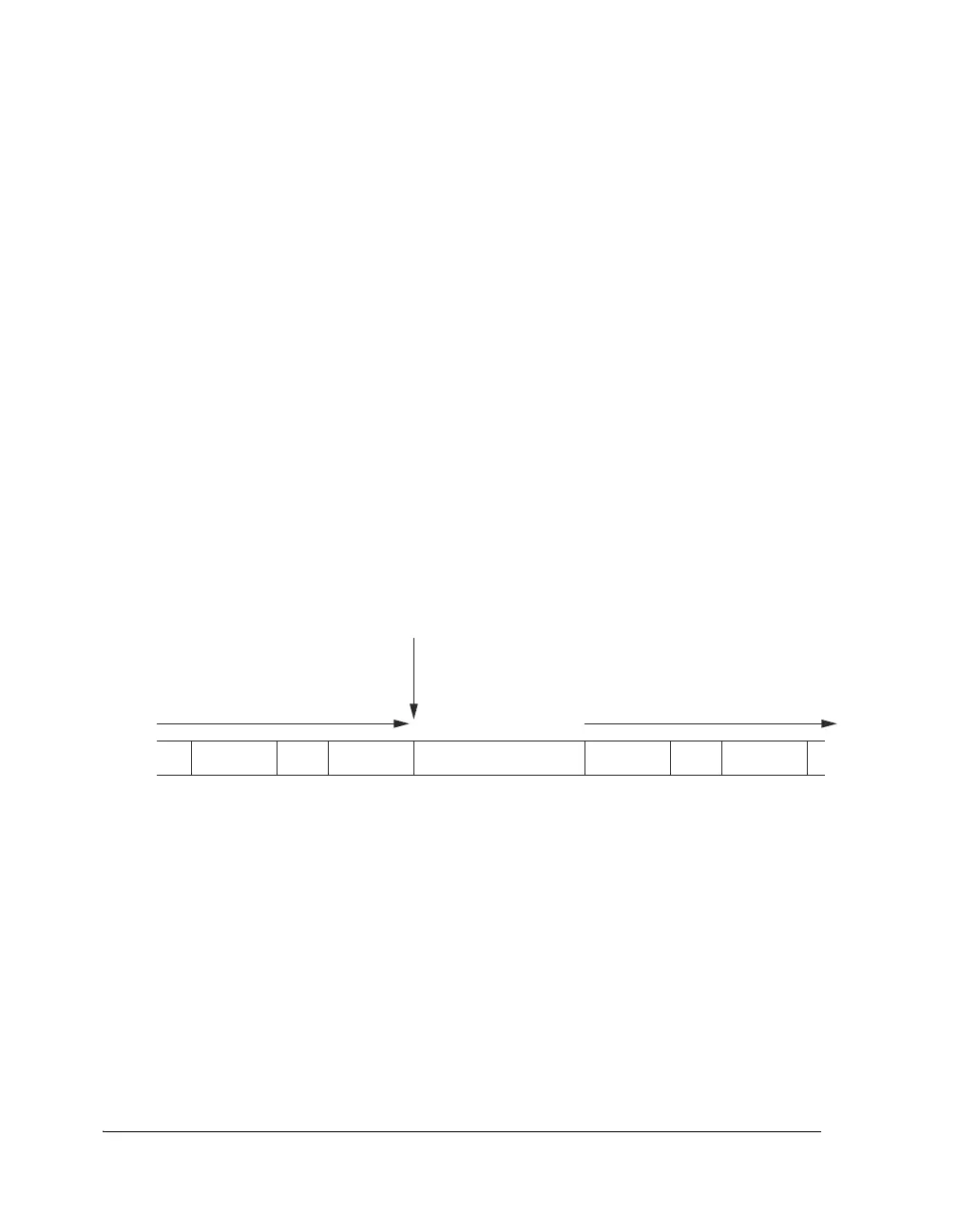

Chained DMA Interrupts

For chained DMA, the channel generates interrupts in one of two ways:

1. If

PCI = 1, (bit 19 of the chain pointer register is the program con-

trolled interrupts, or PCI bit) an interrupt occurs for each DMA in

the chain.

2. If PCI = 0, an interrupt occurs at the end of a completed chain. For

more information on DMA chaining, see “Functional Description”

on page 2-22.

Figure 2-4 shows the PCI timing during TCB loading. After the DMA

count for the last word of frame N becomes zero, the PCI interrupt is

latched. At the same time the DMA reloads the TCB for that specific

channel (assuming no higher priority DMA requests). Finally the DMA

channel resumes operation for frame N–1.

By clearing a channel’s PCI bit during chained DMA, programs

mask the DMA complete interrupt for a DMA process within a

chained DMA sequence.

Transfer Completion Types

The next two sections describe the two types of interrupts that are used to

signal interrupt completion. These are based on the type of peripheral

used.

Figure 2-4. DMA Chaining

DMA Channel

TCB Loading

DMA

Count=1

PCI INTERRUPT

LATCHED FOR

FRAME N

FRAME N FRAME N

-

1

IOD BUS

DMA

Count=N

-

1

DMA

Count=N

DMA

Count=0

Loading...

Loading...