DMA Channel Registers

2-8 ADSP-214xx SHARC Processor Hardware Reference

Extended DMA Parameter Registers

This section describes the enhanced parameter registers used for Accelera-

tor and External Port.

Base registers. These registers, shown in Table 2-6, base registers indicate

the start address of the circular buffer to be transferred to/from memory

on the corresponding DMA channel.

Length registers. These registers, shown in Table 2-7, define the length of

the circular buffer to be transferred to/from memory on the corresponding

DMA channel.

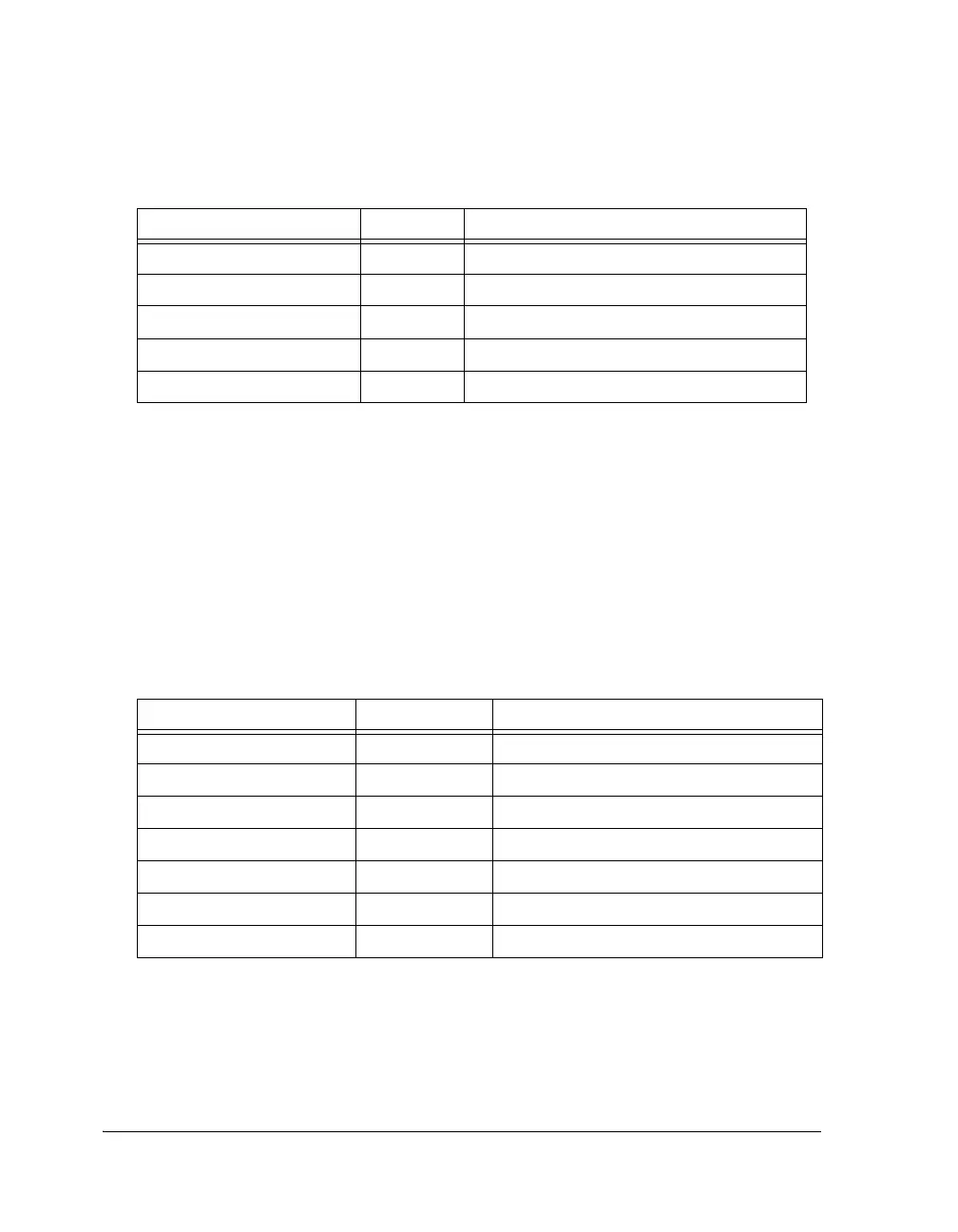

CPFIR 20 Accelerator FIR

CPIIR 20 Accelerator IIR

CPIFFT 21 Accelerator FFT input

CPOFFT 20 Accelerator FFT output

CPEP0–1 21 External Port

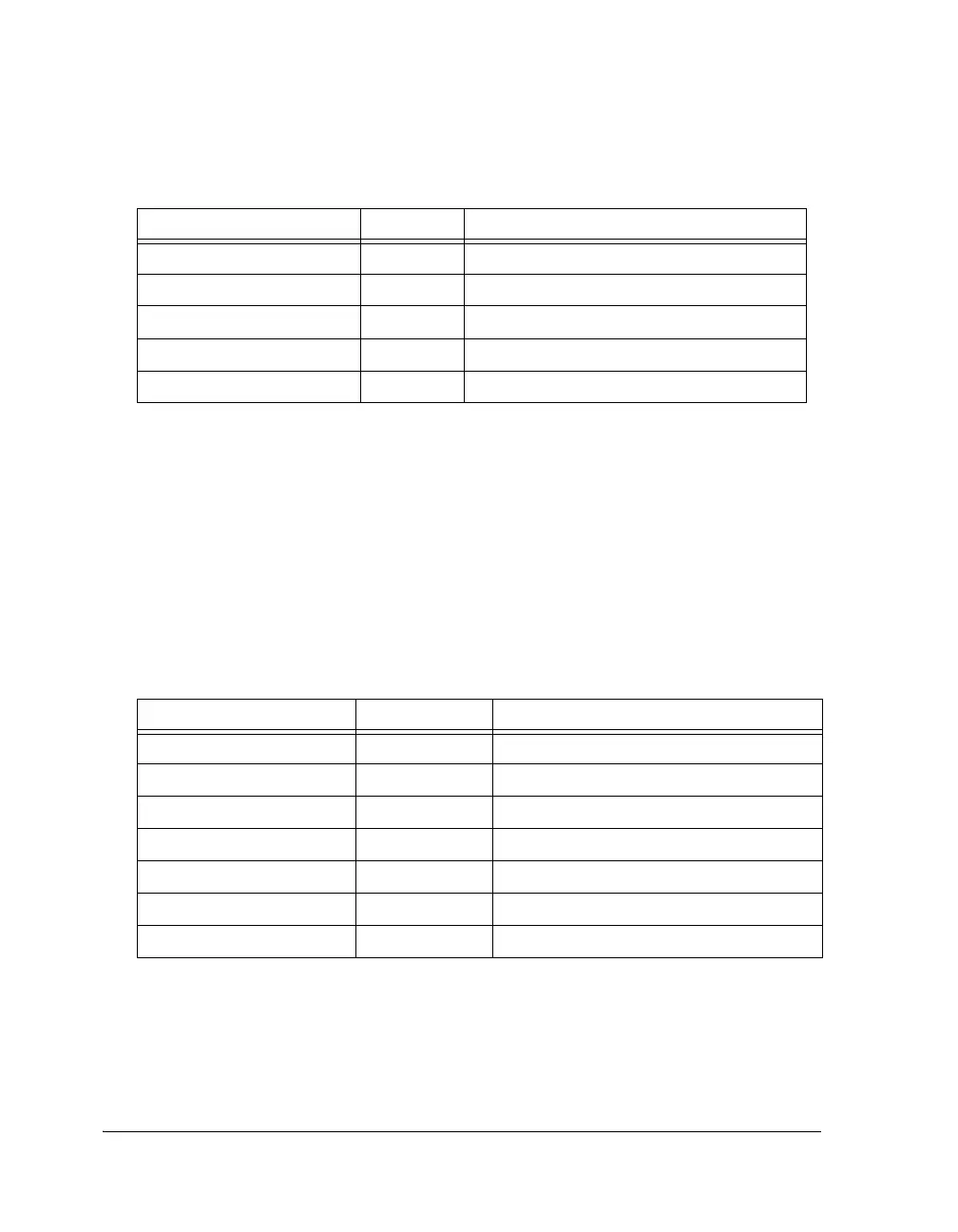

Table 2-6. Base Registers

Register Name Width (Bits) Description

IBFIR 19 Accelerator FIR input

OBFIR 19 Accelerator FIR output

IBIIR 19 Accelerator IIR input

OBIIR 19 Accelerator IIR output

IBFFT 19 Accelerator FFT input

OBFFT 19 Accelerator FFT output

EBEP0–1 28 External Port (external base)

Table 2-5. Chain Pointer Registers (Cont’d)

Register Name Width (Bits) Description

Loading...

Loading...