Interrupts

3-114 ADSP-214xx SHARC Processor Hardware Reference

Interrupts

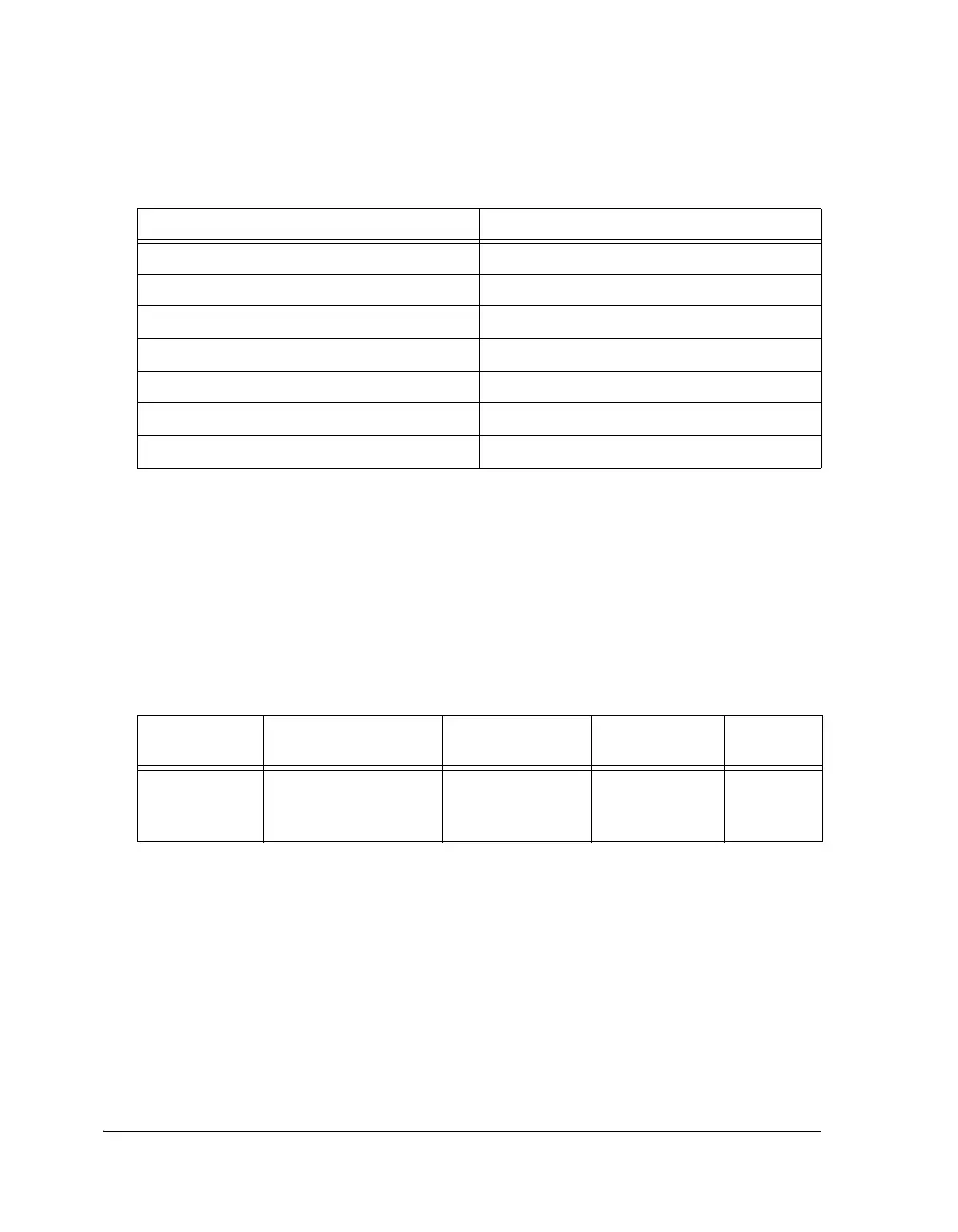

There are two external port DMA channels. The following sections

describe the two ways of triggering interrupts. Table 3-28 provides an

overview of external port interrupts.

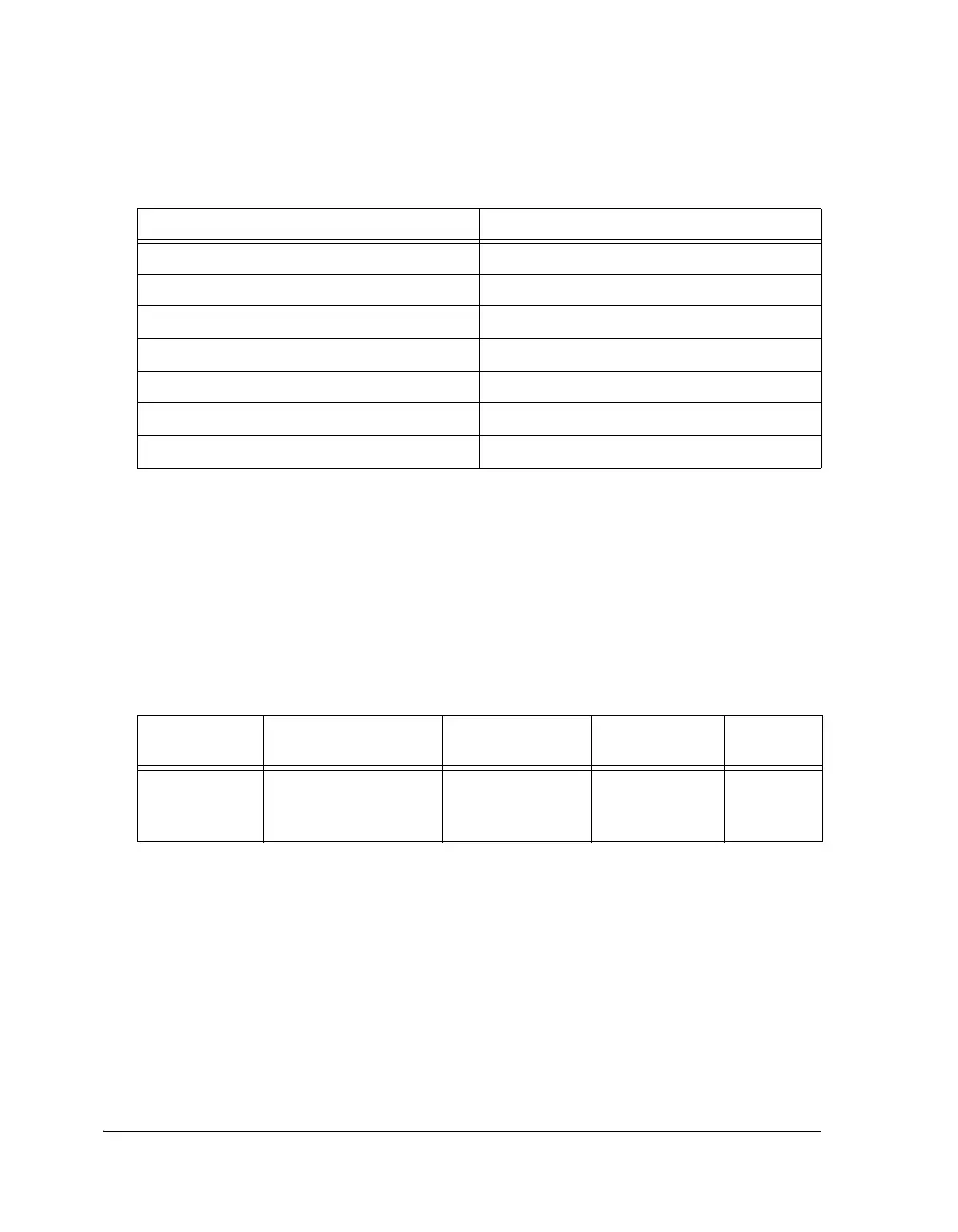

Table 3-27. External Read Index Calculation Delay Line DMA

Equation Result

EIEP + TL[N] First read address for tap N

EIEP + TL[N] + 1 × RMEP Second read address for tap N

EIEP + TL[N] + 2 × RMEP Third read address for tap N

...

EIEP + TL[N] + RCEP × RMEP Last read address for tap N

EIEP + TL[N + 1] First read address for tap N + 1

EIEP + TL[N + 1] + 1 × RMEP Second read address for tap N + 1

Table 3-28. External Port Interrupt Overview

Interrupt Source Interrupt Condition Interrupt

Completion

Interrupt

Acknowledge

Default IVT

External port

DMA (2 chan-

nels)

DMA RX/TX complete –internal transfer

completion

–access completion

RTI instruction P9I, P13I

Loading...

Loading...