ADSP-214xx SHARC Processor Hardware Reference 14-3

Precision Clock Generator

• Bypass mode for external frame sync manipulation

• External trigger mode starts PCG operation. No additional jitter

introduced since operation is independent of the on-chip PLL by

using off-chip clocks.

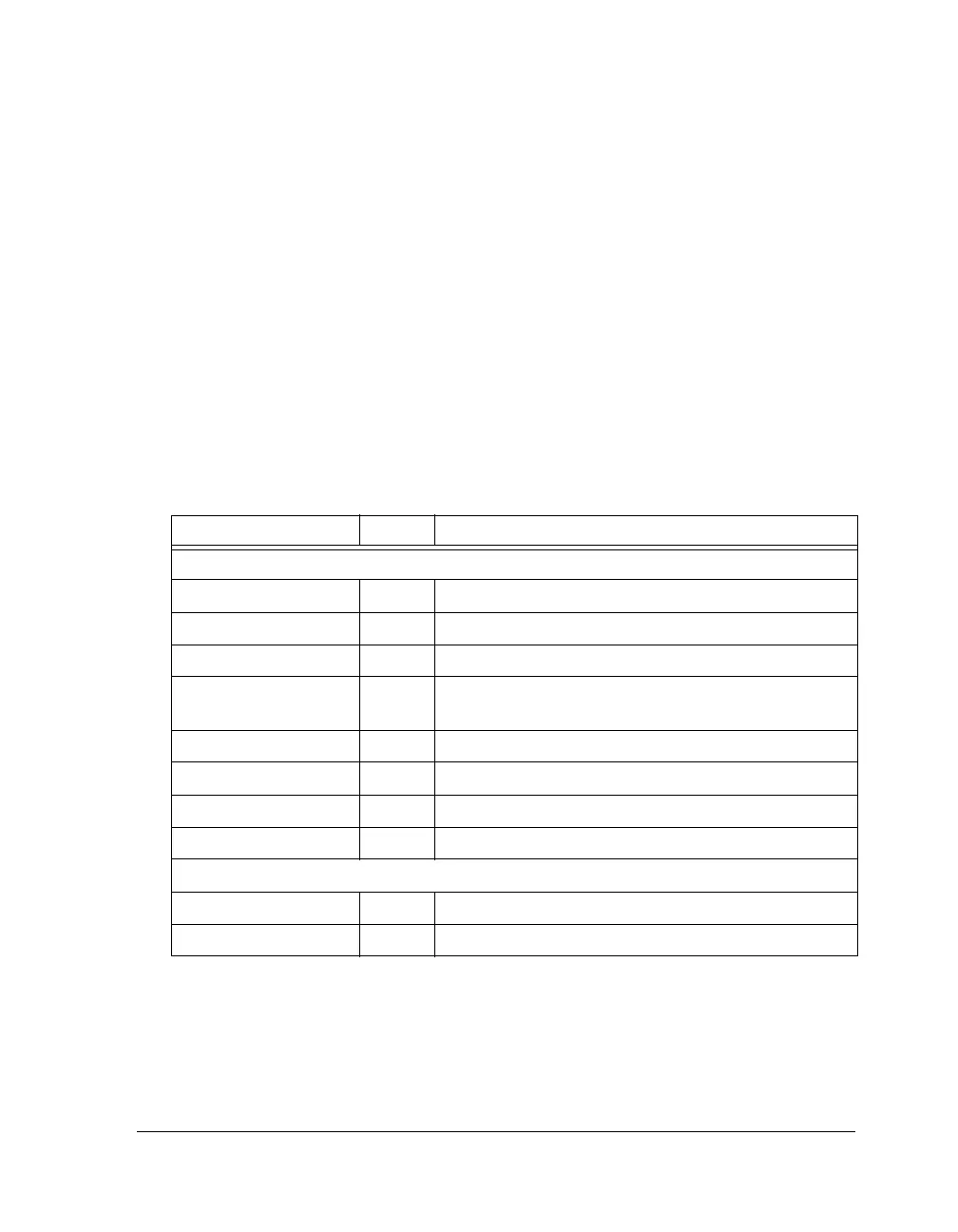

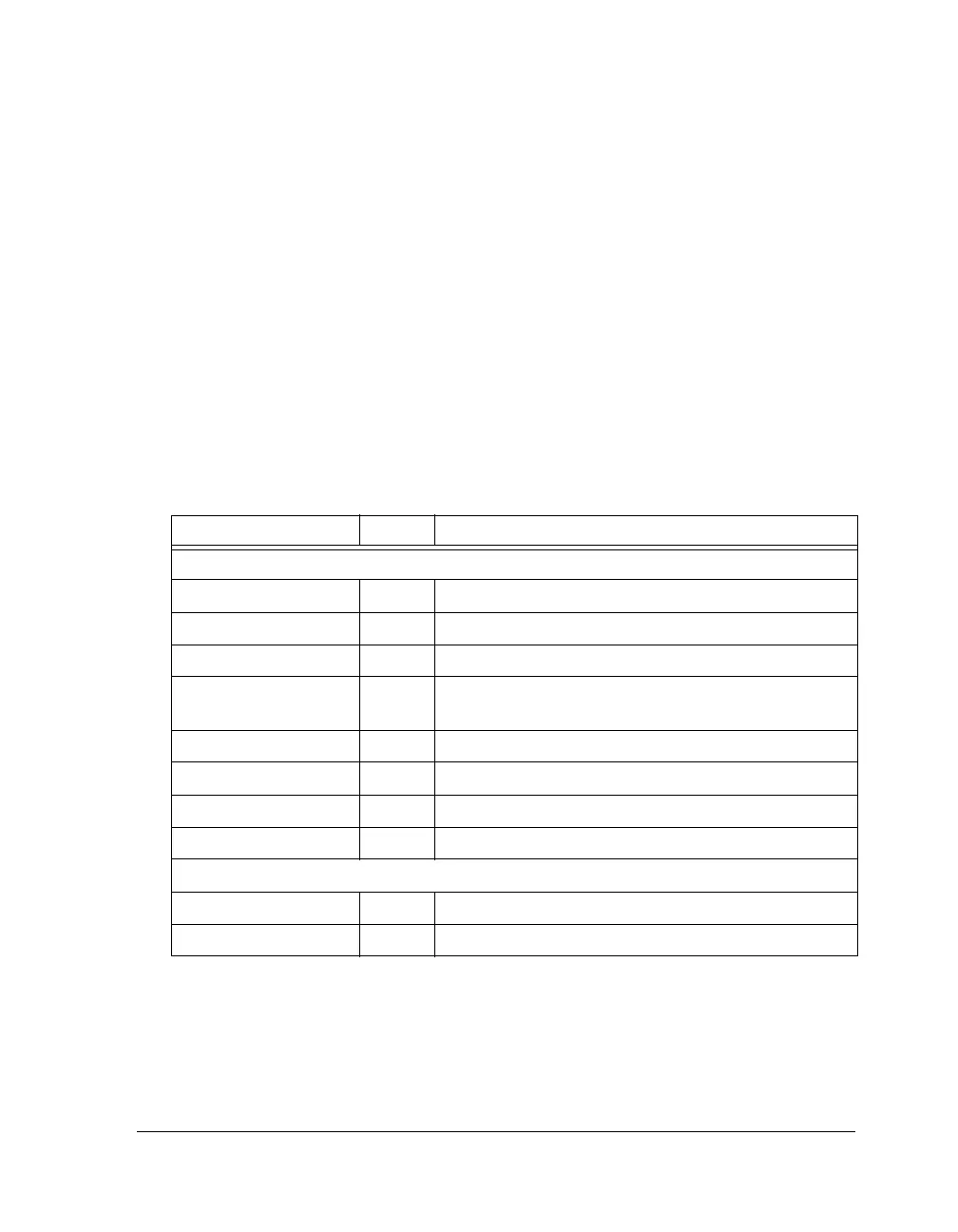

Pin Descriptions

Table 14-2 provides the pin descriptions for the PCGs. Note x = unit

A/B/C/D.

Table 14-2. PCG Pin Descriptions

Internal Nodes I/O Description

Inputs

CLKIN I External clock input for PCG x

PCLK I Internal peripheral clock input for PCG x

PCG_SYNC_CLKx_I I External trigger used to enable the frame sync output

PCG_EXTx_I I External clock A input provided to the PCG x (not

CLKIN)

MISCA2_I I External frame sync used for bypass mode PCG A

MISCA3_I I External frame sync used for bypass mode PCG B

MISCA4_I I External frame sync used for bypass mode PCG C

MISCA5_I I External frame sync used for bypass mode PCG D

Outputs

PCG_CLKx_O O Serial clock x output

PCG_FSx_O O Frame sync x output

Loading...

Loading...