ADSP-214xx SHARC Processor Hardware Reference 2-1

2 I/O PROCESSOR

In applications that use extensive off-chip data I/O, programs may find it

beneficial to use a processor resource other than the processor core to per-

form data transfers. The ADSP-214xx processors contain an I/O processor

(IOP) that supports a variety of DMA (direct memory access) operations.

Each DMA operation transfers an entire block of data. These operations

include the transfer types shown in Table 2-1 and the list that follows.

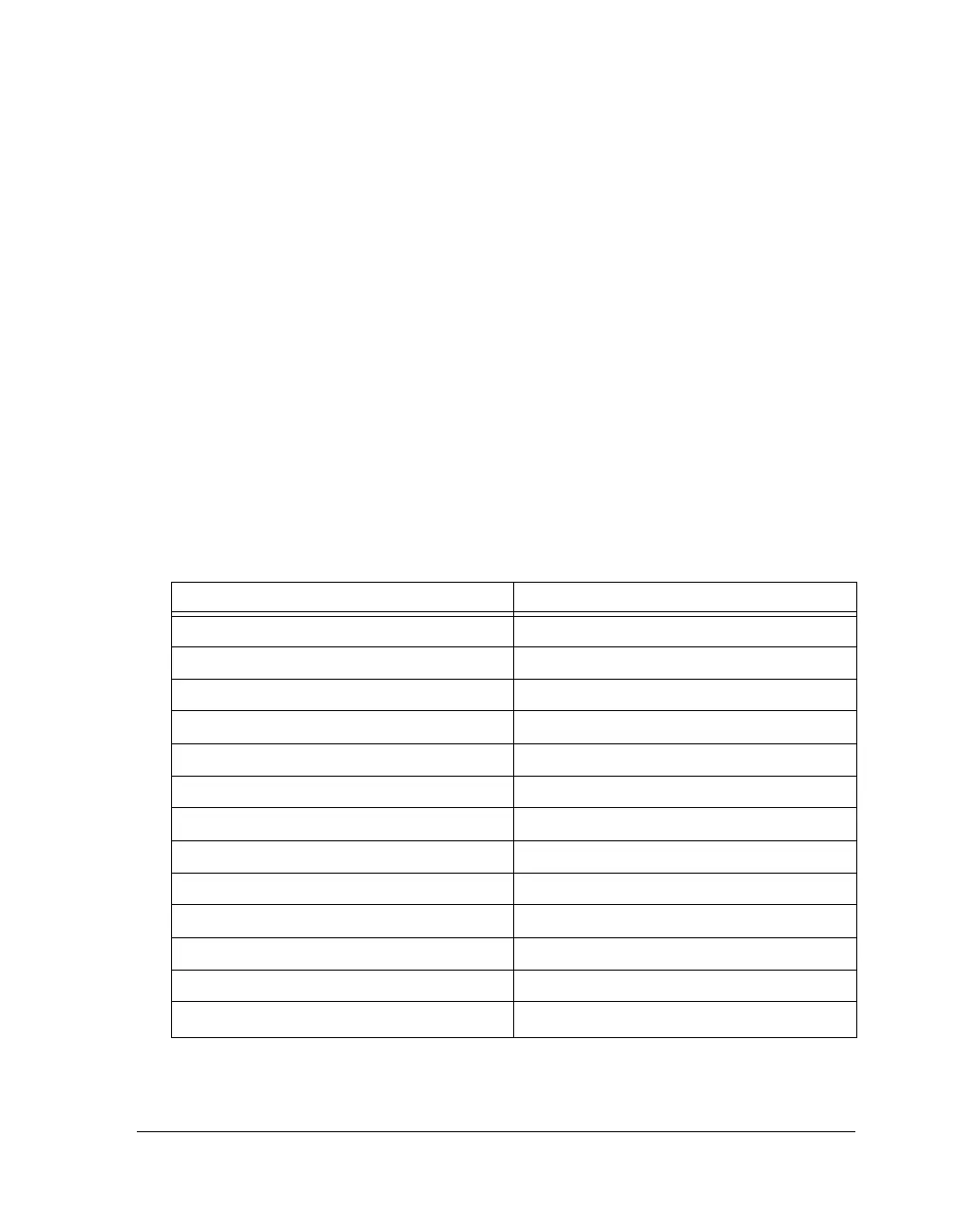

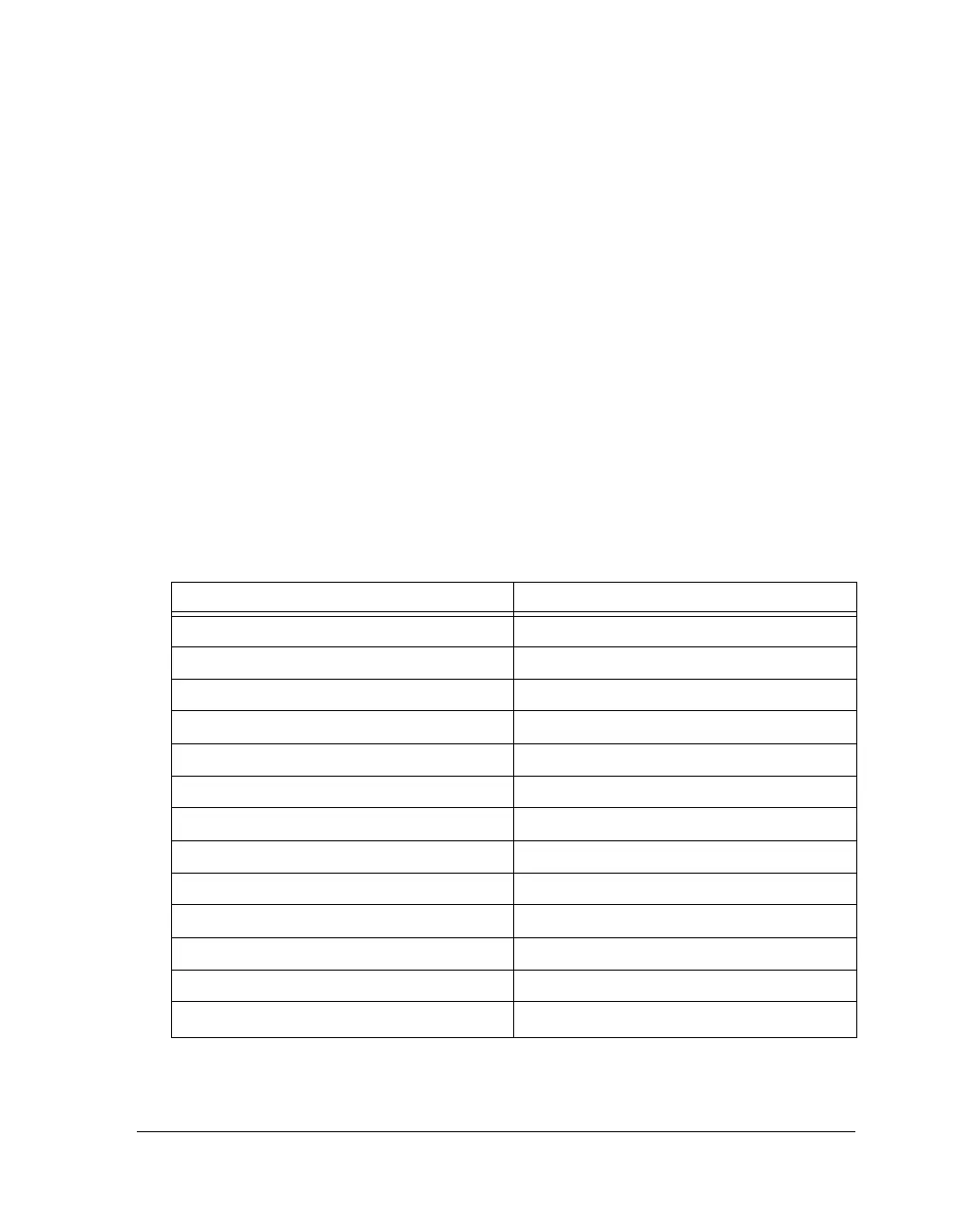

Table 2-1. I/O Processor Specifications

Feature Availability

Total DMA channels See product specific data sheet

Rotating DMA channel priority Yes

Media Local Bus (MLB) 31

SPORT DMA channels 16

IDP DMA channels 8

UART DMA channels 4

FIR/FFT/IIR DMA channels 2

SPI DMA channels 2

MTM/DTCP DMA channels 2

External Port DMA channels 2

PDAP DMA channel 1

DMA channel interrupts 16

Clock Operation f

PCLK

Loading...

Loading...