DDR2 DRAM Controller (ADSP-2146x)

3-72 ADSP-214xx SHARC Processor Hardware Reference

Force Activation Window

Traditionally, SDRAM has operated with a maximum of 4 internal banks.

However, with DDR2 some higher-density devices will support 8 individ-

ual banks. For this reason, JEDEC has limited the number of banks that

may be activated within a set period.

DDR2 devices support a new timing parameter called four active banks

window (t

FAW

). This is the minimum amount of time that must pass

before more than four ACTIVE (ACT) commands may occur. It is accept-

able to have more than 4 banks open simultaneously, but the additional

ACT command(s) must be spaced out past the t

FAW

(min) window. As

shown in Figure 3-17, t

RCD

for the fourth opened bank is complete at T8.

To satisfy t

FAW

(min), the fifth ACT command cannot occur until T11.

Furthermore the controller supports four external memory selects contain-

ing each DDR2. All external banks (

DDR2_CSx) provide multibank

support, so the maximum number of open pages is 8 x 4 = 32 pages.

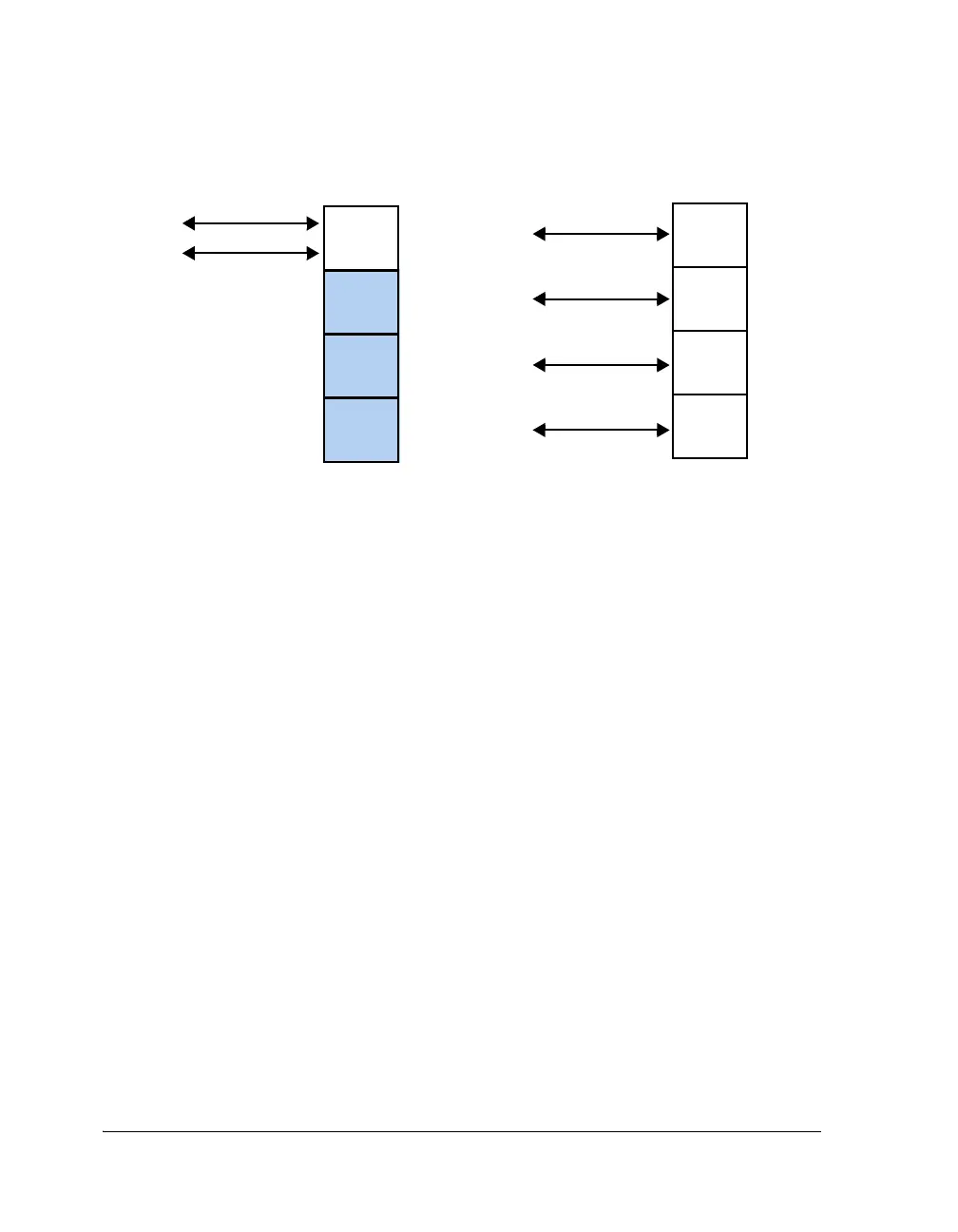

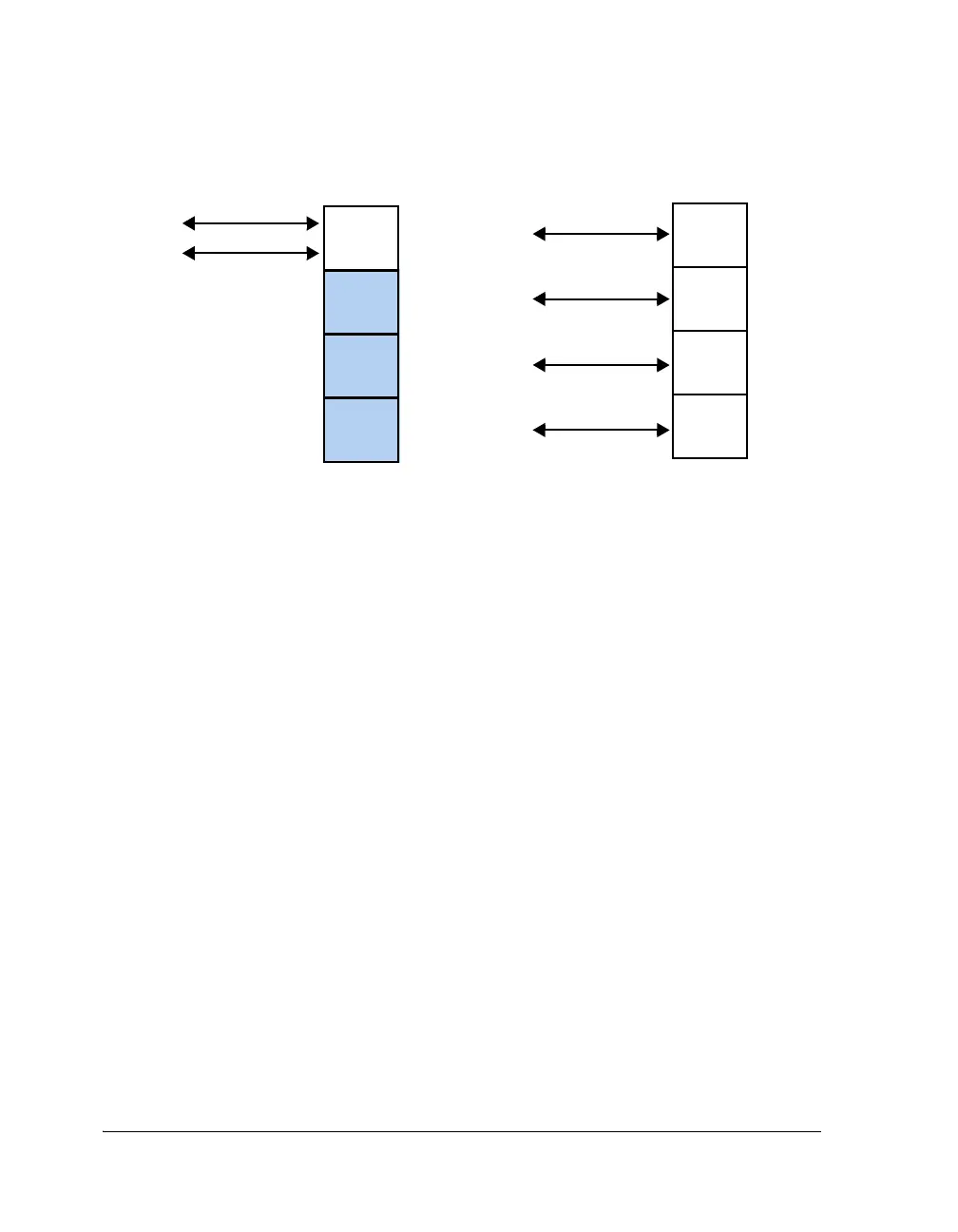

Figure 3-16. Single Versus Multibank Access

Bank A

Bank B

Bank C

Bank D

Bank A

Bank B

Bank C

Bank D

Access to page x

Access to page y

Access to page x

Access to page y

Access to page x

Access to page y

Single bank access Multibank access

Loading...

Loading...