ADSP-214xx SHARC Processor Hardware Reference 11-9

Input Data Port

PDAP Port Selection

The input to channel 0 of the IDP is multiplexed, and may be used either

in the serial mode or in a direct parallel input mode. Setting the PDAP_EN

bit high disables the connection of SIP0 to channel 0 of the FIFO. The

data inputs can come either from the DAI pins or the external port ADDR

pins. This is selected by the PDAP_PP_SELECT bit in the PDAP_CTL register.

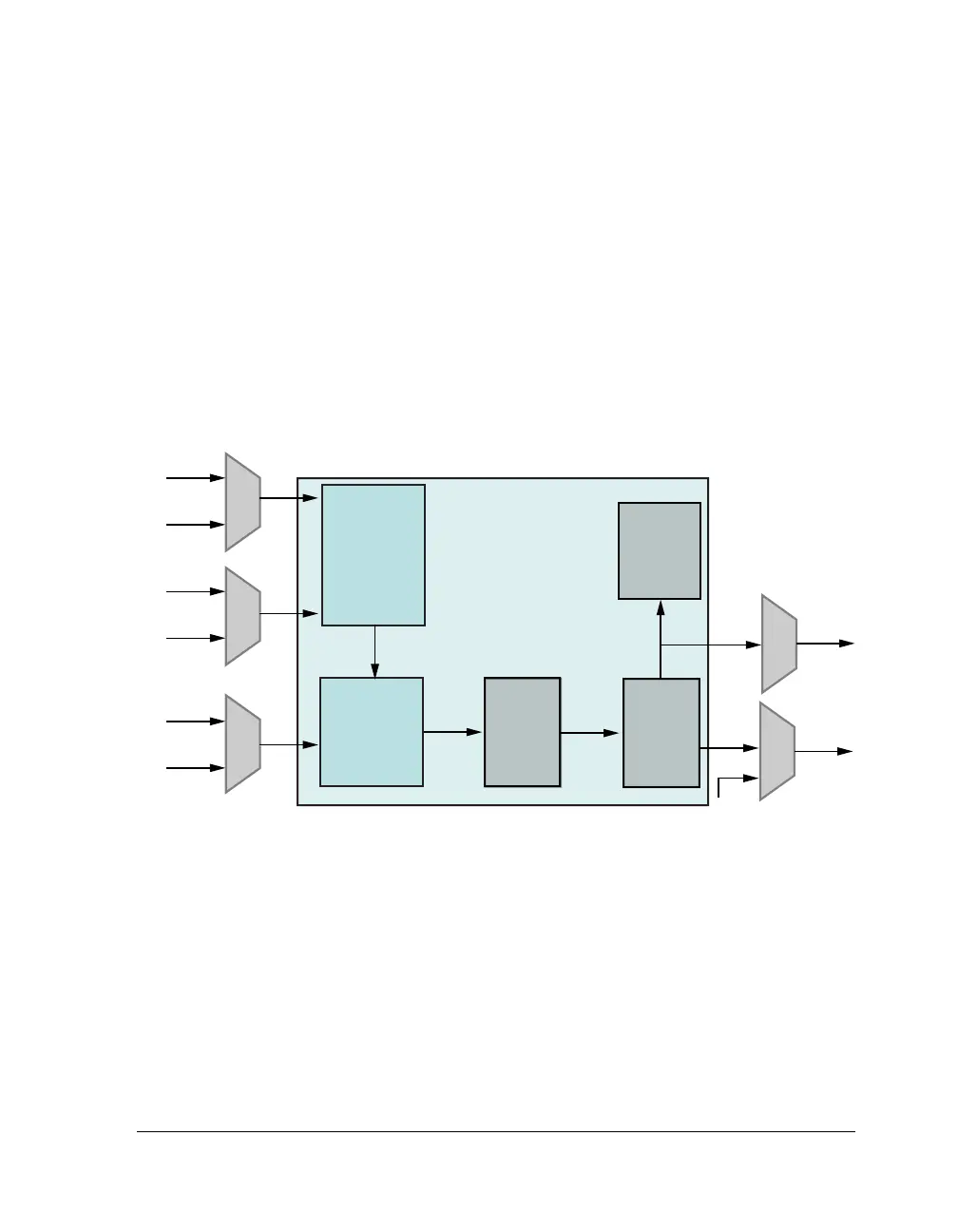

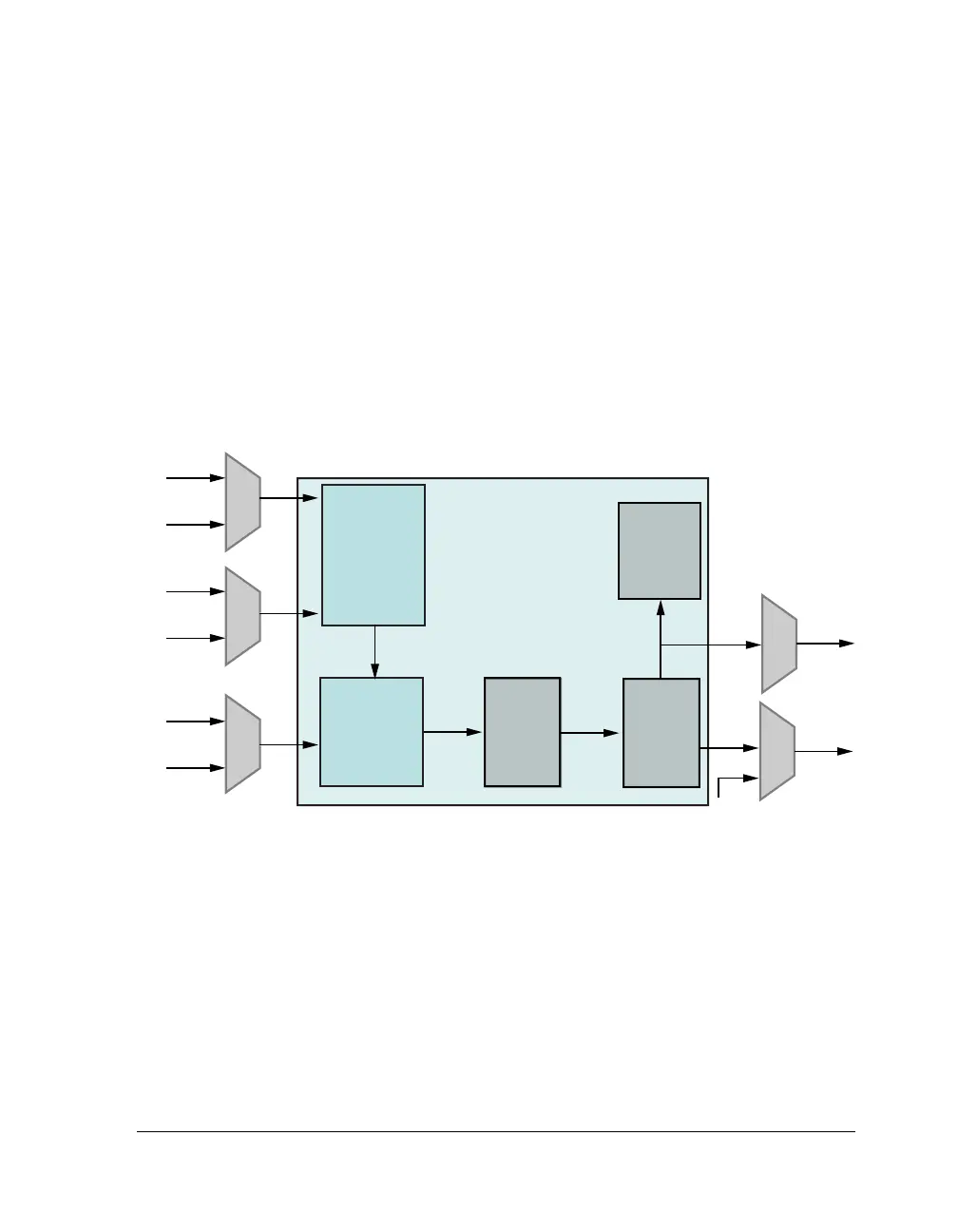

Figure 11-2 illustrates the data flow for IDP channel 0, where either the

PDAP or serial input can be selected.

Data Hold

When the PDAP_HOLD signal is high, all latching clock edges are ignored

and no new data is read from the input pins. The packing unit operates as

normal, but it pauses and waits for the PDAP_HOLD signal to be deasserted

and waits for the correct number of distinct input samples before passing

the packed data to the FIFO.

Figure 11-2. PDAP Port (Detail of IDP Channel 0)

IDP_FIFO

DATA10

PDAP Control

IDP0_CLK_I

PDAP_CLK_I

DATA11

IDP0_FS_I

PDAP_HOLD_I

DATA31

-

12

DAI_PB20

-

1

INPUT DATA

LATCH

CHANNEL 0

DATA8

PDAP_STRB_O

DATA

MASK

UNIT

DAI

UNIT

32-BIT

DATA

PACKING

UNIT

SIP

DATA

Loading...

Loading...