Features

9-2 ADSP-214xx SHARC Processor Hardware Reference

Features

The DAI/DPI incorporates a set of peripherals and a very flexible routing

(connection) system permitting a large combination of signal flows. A set

of DAI/DPI-specific registers make such design, connectivity, and func-

tionality variations possible. All routing related to peripheral states for the

DAI interface is specified using DAI/DPI registers. For more information

on pin states, refer to “I/O Pin Buffers” on page 9-7.

The DAI/DPI may be used to connect combinations of inputs to combi-

nations of outputs. This function is performed by the SRU/SRU2 via

memory-mapped control registers.

This virtual connectivity design offers a number of distinct advantages:

• Flexibility

• Increased numbers and kinds of configurations

• Connections can be made via software—no hard wiring is required

Inputs may only be connected to outputs.

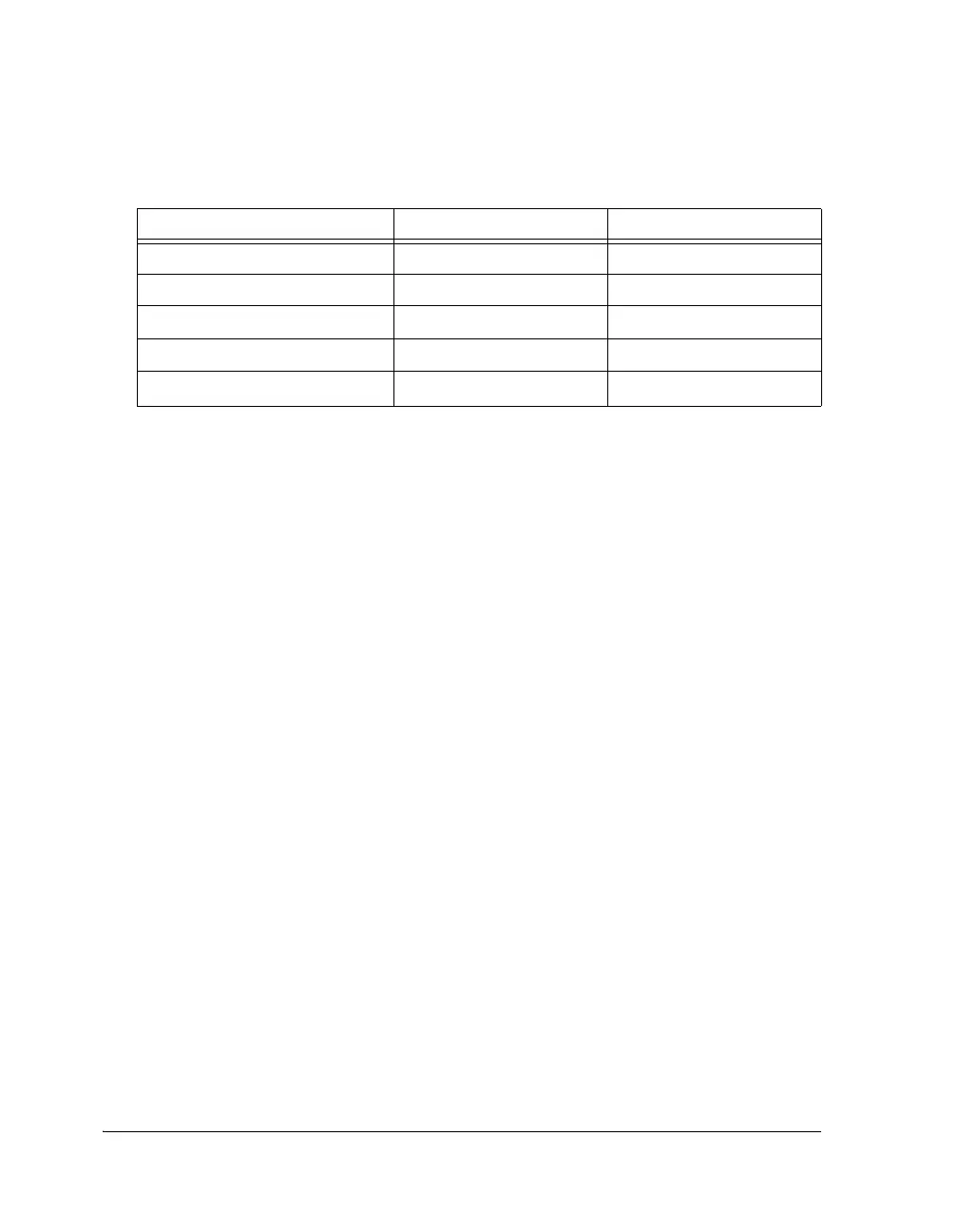

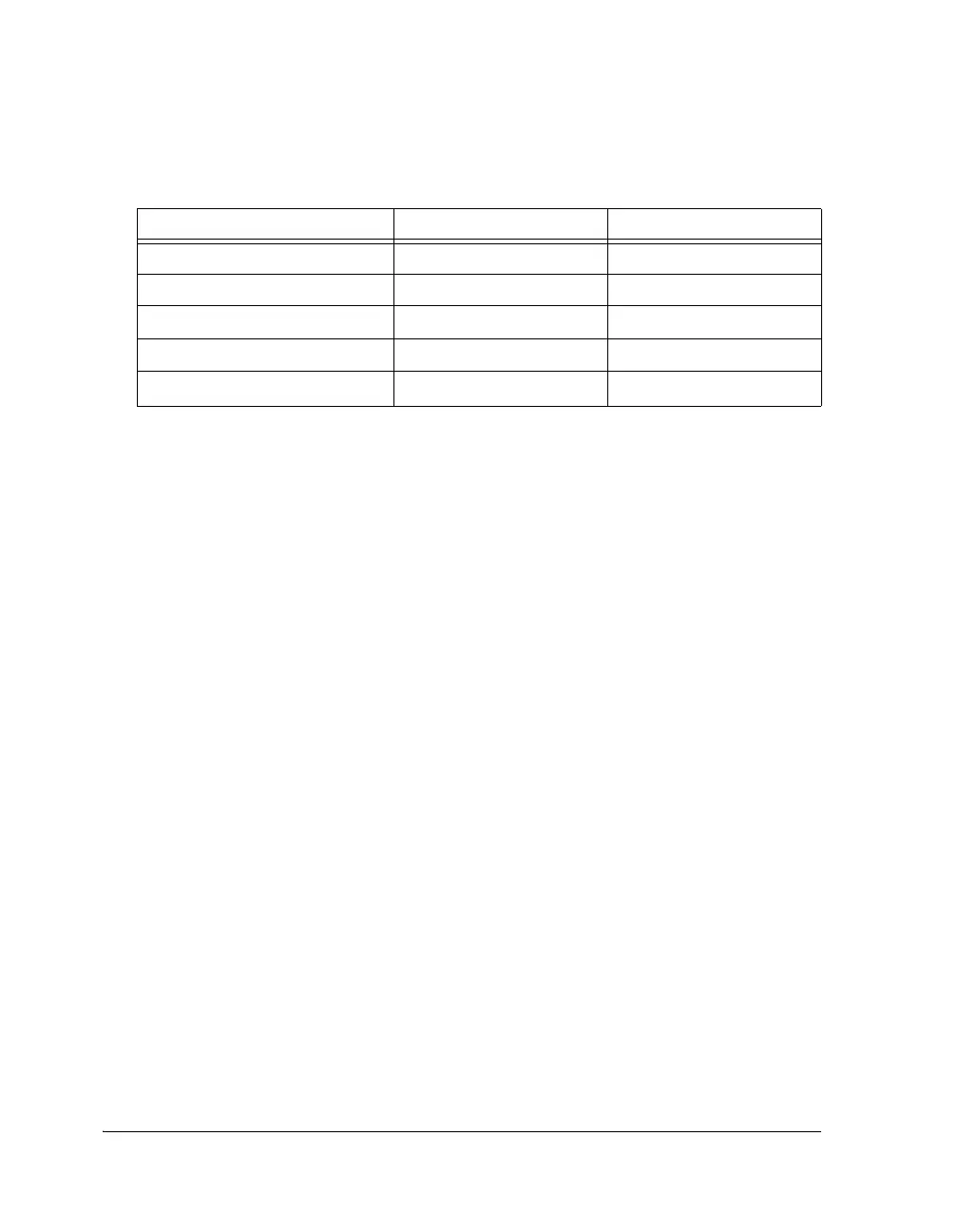

Total Channels 32 12

Miscellaneous I/O channels 10 9

Peripheral Channels 22 3

Local Memory No No

Clock Operation f

PCLK

/4 f

PCLK

/4

Table 9-1. Routing Unit Specifications (Cont’d)

Feature DAI DPI

Loading...

Loading...