ADSP-214xx SHARC Processor Hardware Reference A-45

Registers Reference

ADSP-2147x, ADSP-2148x External Port

Registers

The registers in the following sections are specific to the ADSP-2147x and

the ADSP-2148x external port and include the external port, the SDRAM

controller, and AMI registers.

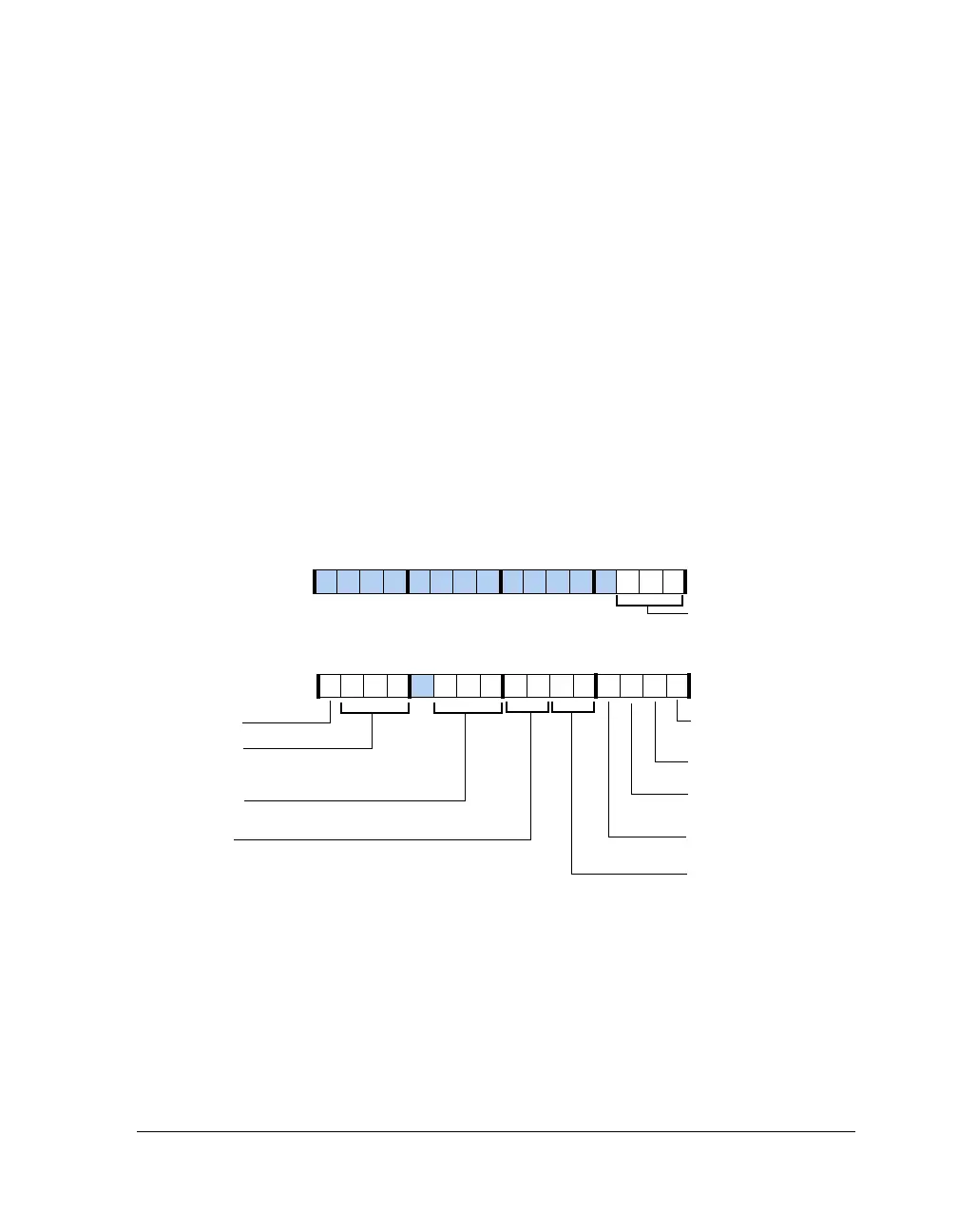

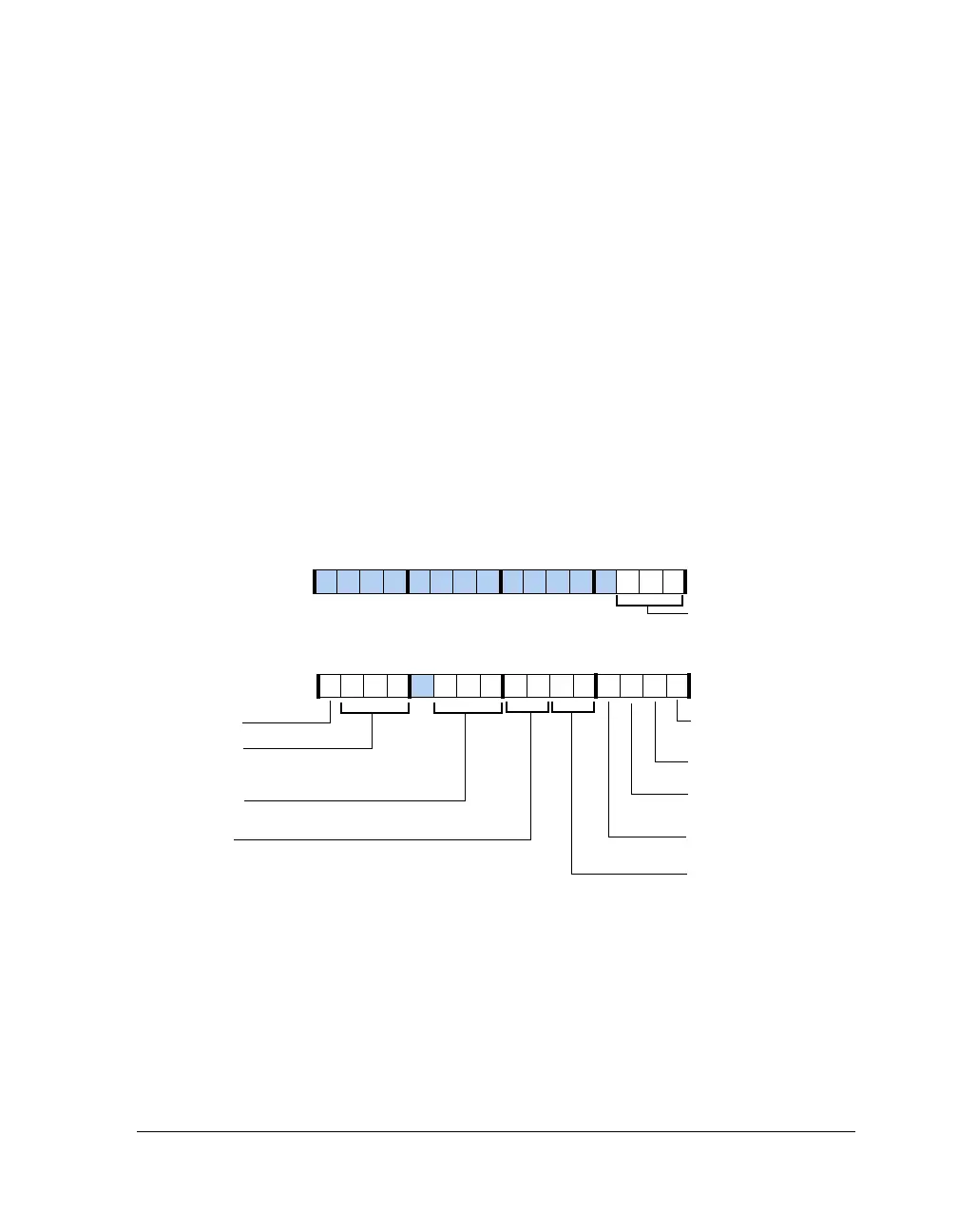

External Port Control Register (EPCTL)

The external port control register can be programmed to arbitrate the

accesses between the processor core and DMA, and between different

DMA channels. These registers are shown in Figure A-20 and described in

Table A-25.

Figure A-20. EPCTL Register

B0SD

Bank 0 SDRAM

B1SD

Bank 1 SDRAM

B2SD

Bank 2 SDRAM

B3SD

Bank 3 SDRAM

DMAPR (7–6)

DMA Channel Priority for CH0 and CH1

EPBR (5–4)

External Port Bus Priority

FRZDMA (10–8)

Arbitration Freezing Length for DMA

FRZCR (14–12)

Arbitration Freezing Length for

CORE Accesses

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

DATEN (15–18)

EP Data Mask Enable

DATEN (15–18)

09 837564 2114 12 11 101315

Loading...

Loading...