ADSP-2146x External Port Registers

A-18 ADSP-214xx SHARC Processor Hardware Reference

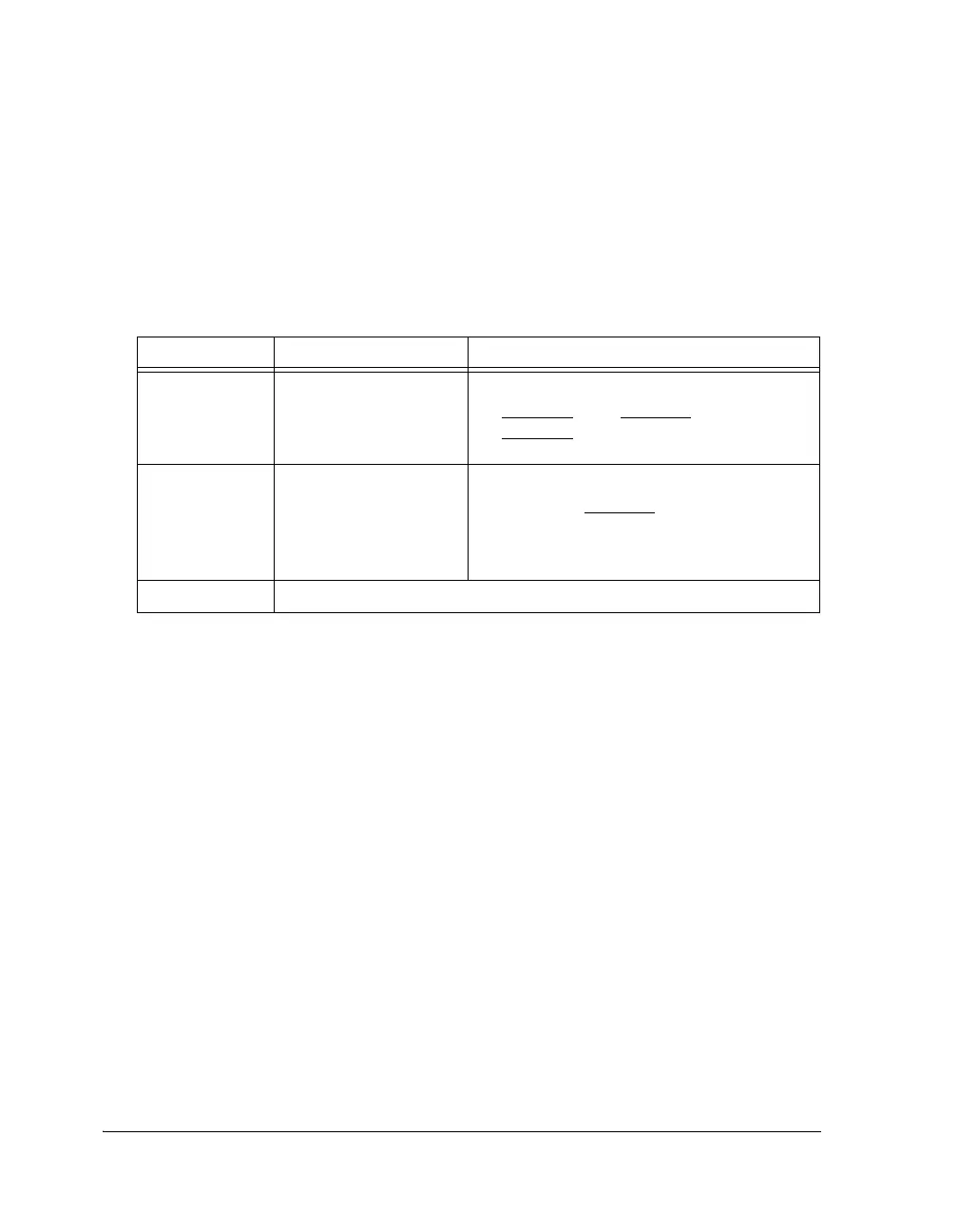

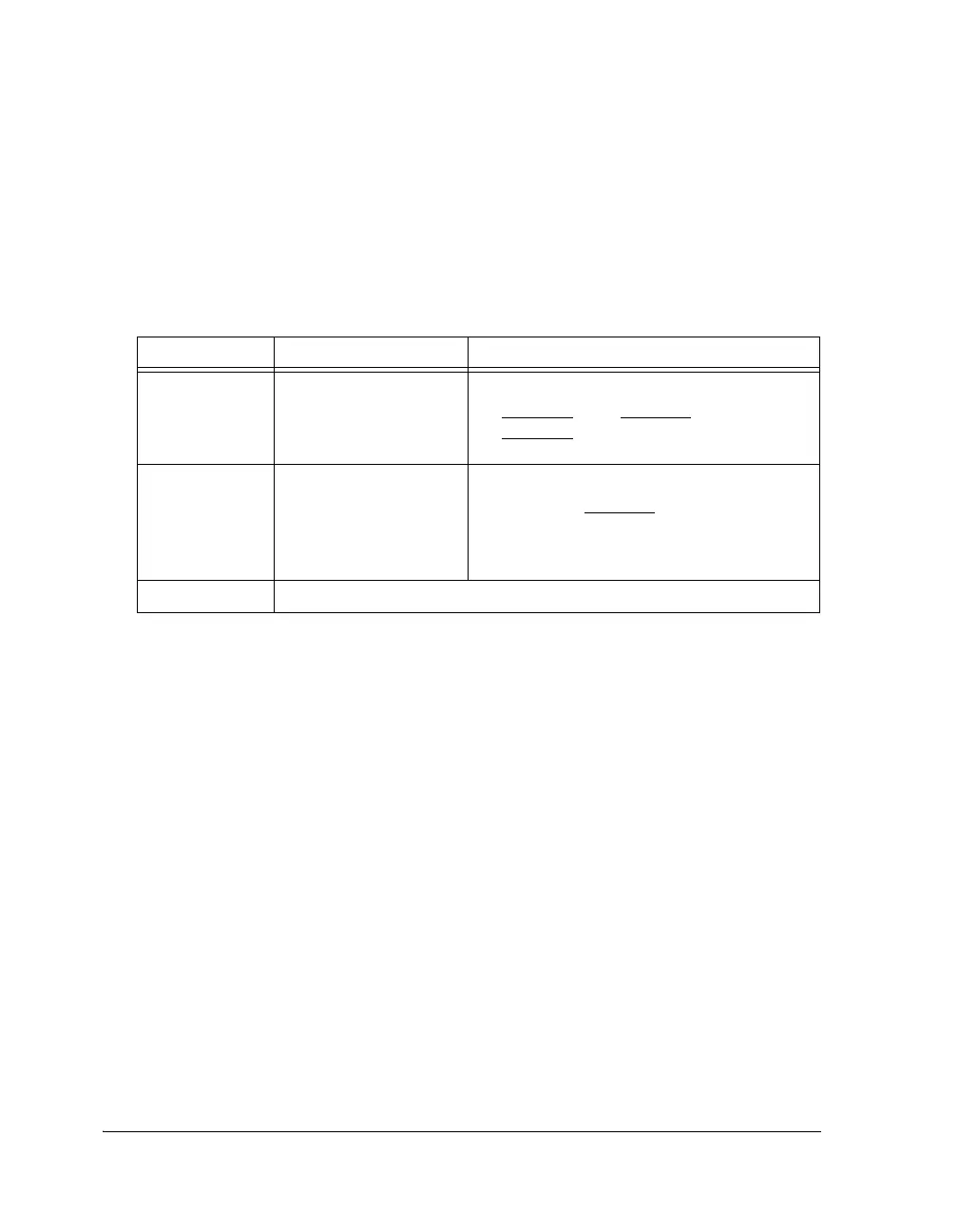

Running Reset Control Register (RUNRSTCTL)

The RUNRSTCTL register is used to control the running reset functionality

and is described in Table A-7.

ADSP-2146x External Port Registers

The registers in the following sections are specific to the ADSP-2146x

external port and include the external port, the DDR2 controller, and

AMI registers.

External Port Control Register (EPCTL)

The following registers are used to control asynchronous memory inter-

face (AMI), the DDR2 and SDRAM controllers, and the shared memory

interface. The external port control register can be programmed to arbi-

trate the accesses between the processor core and DMA, and between

different DMA channels. These registers are shown in Figure A-6 and

described in Table A-8.

Table A-7. Running Reset Control Register Bit Descriptions (RW)

Bit Name Description

0PM_RUNRST_PINENConfigures the RESETOUT pin for RUNRST

input.

0 =

RESETOUT pin is RESETOUT

1 = RESETOUT pin is RUNRST input

1PM_RUNRST_ENEnable the Running Reset Functionality. If this

bit is cleared, attempting to cause a running reset

by toggling the

RUNRSTIN pin has no affect

0 = Running reset disabled

1 = Running reset enabled

31–2 Reserved

Loading...

Loading...