ADSP-214xx SHARC Processor Hardware Reference 9-25

Digital Application/Digital Peripheral Interfaces

DPI Routing Capabilities

Table 9-2 provides an overview about the different routing capabilities for

the DPI unit.

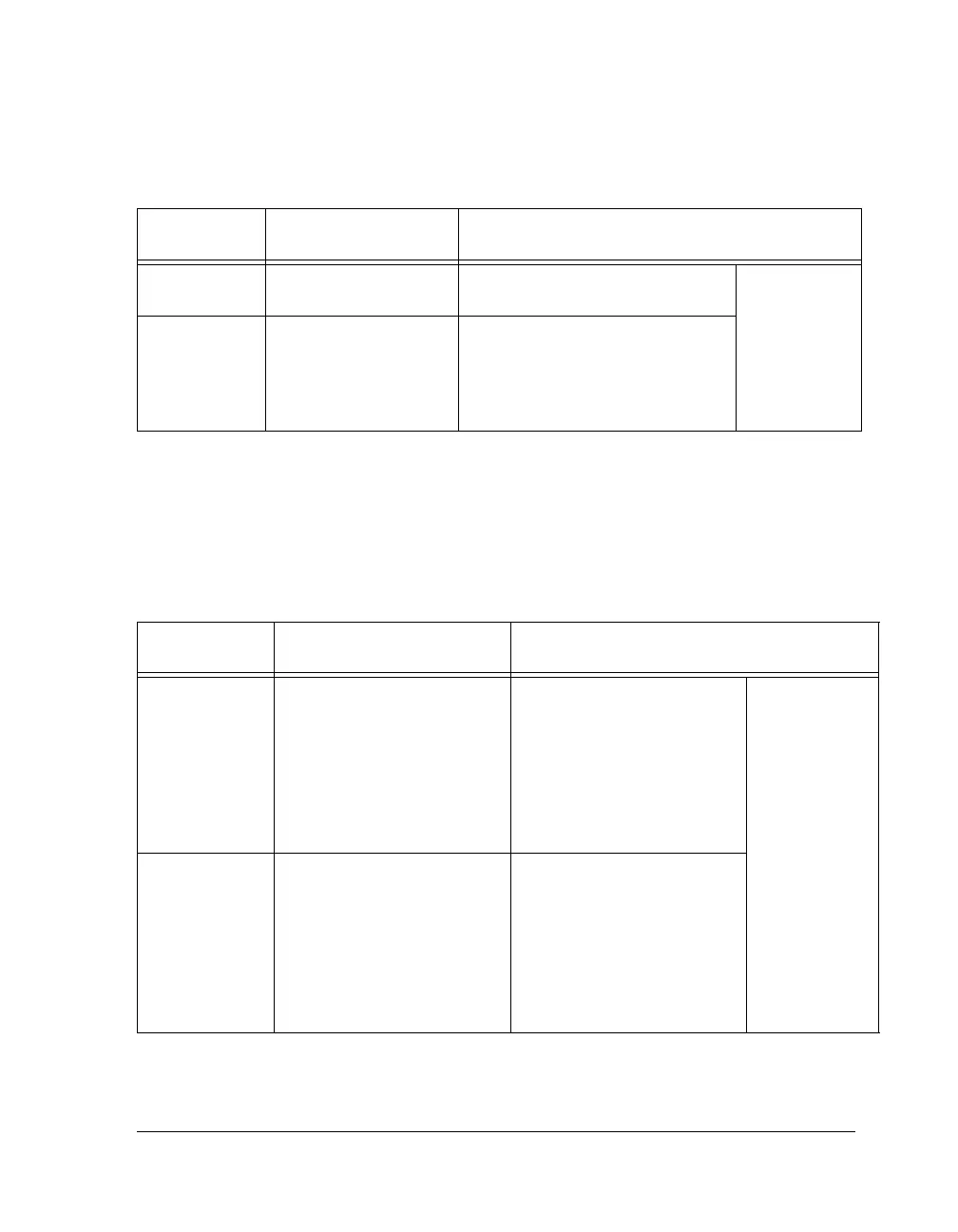

F–Pin Buffer DAI Pin Buffer Enable

20–1

SPORT7–0 (clock, FS, data, TDV)

MISCA5–0

Logic level high

Logic level low

G–Shift Register

(ADSP-2147x

only)

SR_CLK_I

SR_LAT_I

SR_SDI_I

SPORT7-0 (clk, FS)

SPORT7-0 AB (data)

PCG A-B (clk, FS)

DAI Pin Buffer 8-1

SR_CLK, SR_LAT, SR_SDI

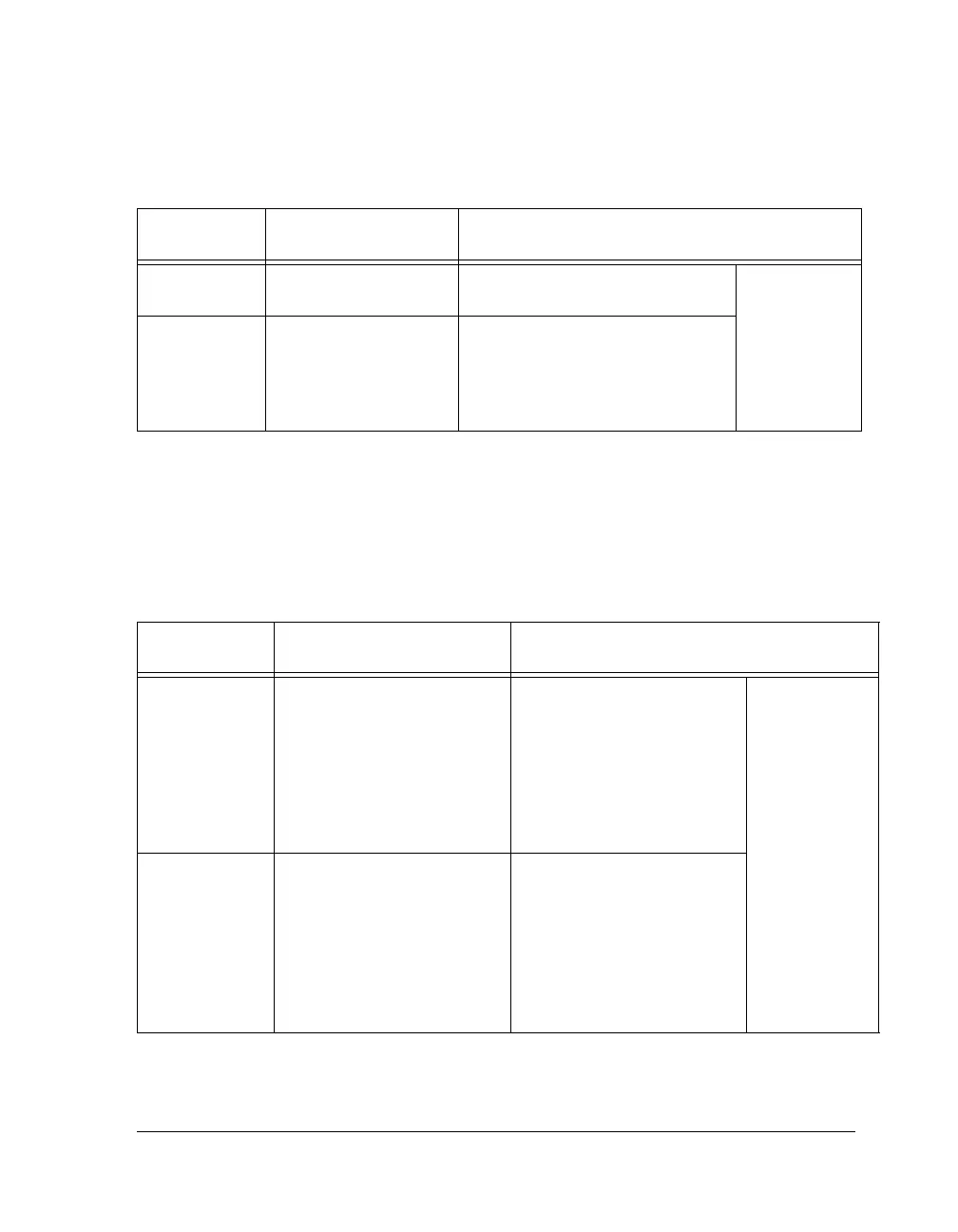

Table 9-5. DPI Routing Capabilities

DPI Group Input (xxxx_I) Output (xxxx_O)

A–Miscellaneous

Signals

SPI (MOSI, MISO, DS, CLK)

SPIB (MOSI, MISO, DS, CLK)

TWI (Clock, Data)

UART0 RX data

Timer1–0

FLAG15–4/PWM3–1

MISCB8–0

DPI Interrupt 13–5

Timer1–0

UART0 TX Data

DPI Pin Buffer

Logic level high

Logic level low

B–Pin Buffer

Input

DPI Pin Buffer Input Timer1–0

UART0 TX data

SPI (MOSI, MISO, DS, CLK,

SPIFLG)

SPIB (MOSI, MISO, DS, CLK,

SPIBFLG)

FLAG15–4/PWM3–1

PCG (C, D) (clock, FS)

Table 9-4. DAI Routing Capabilities

DAI Group Input (xxxx_I) Output (xxxx_O)

Loading...

Loading...