Features

14-2 ADSP-214xx SHARC Processor Hardware Reference

Features

The following list describes the features of the precision clock generators.

• Operates on the DAI and DPI units

• PCG input clock selection from CLKIN, PCLK or external DAI pins

• Provides 4 different clock dividers for serial clock, frame sync,

phase (20-bit) and pulse width (16-bit)

• Phase shift allows adjustment of the frame sync relative to the serial

clock and can be shifted the full period and wrap around

• Provides pulse width control for arbitrary frame sync signal

generation

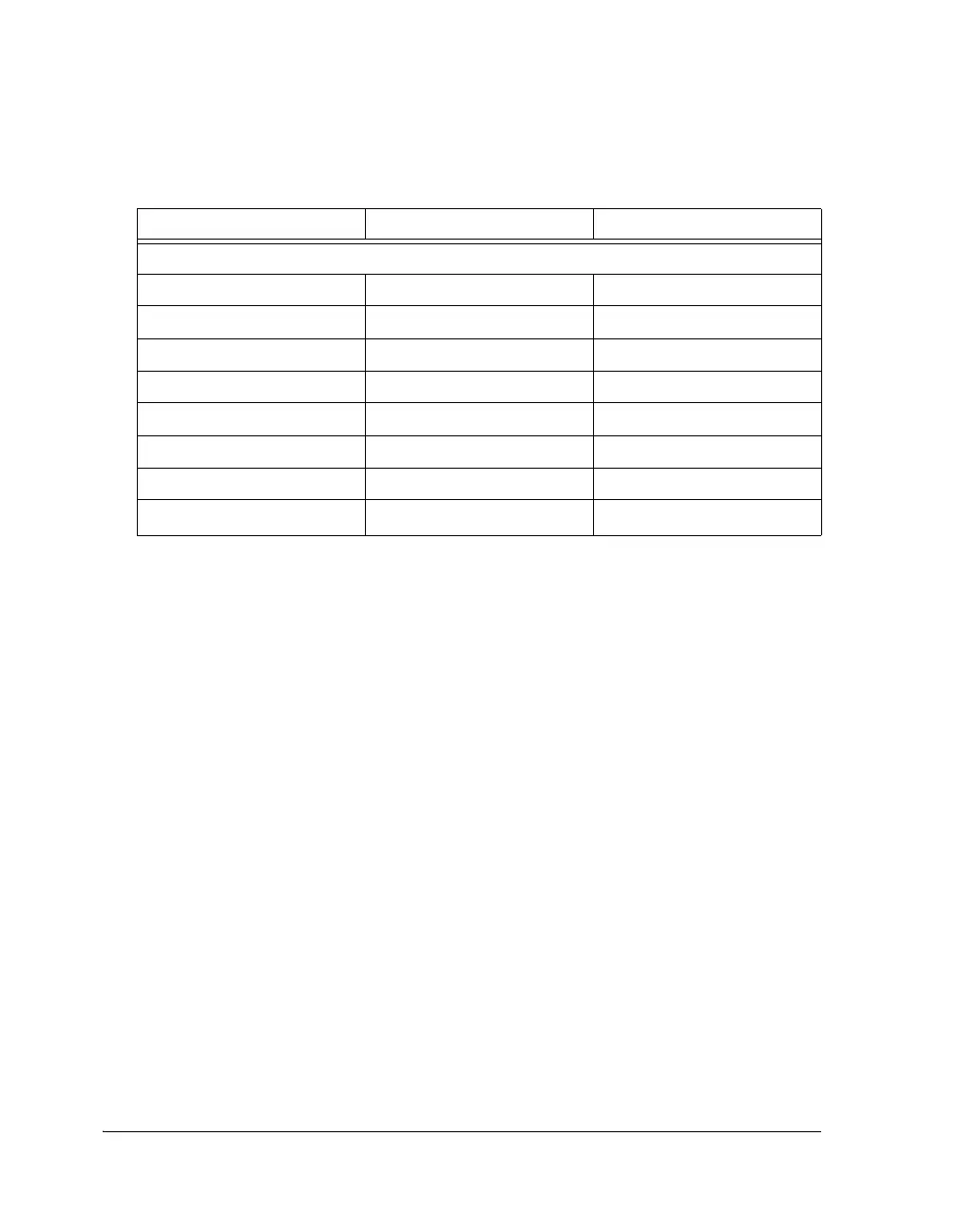

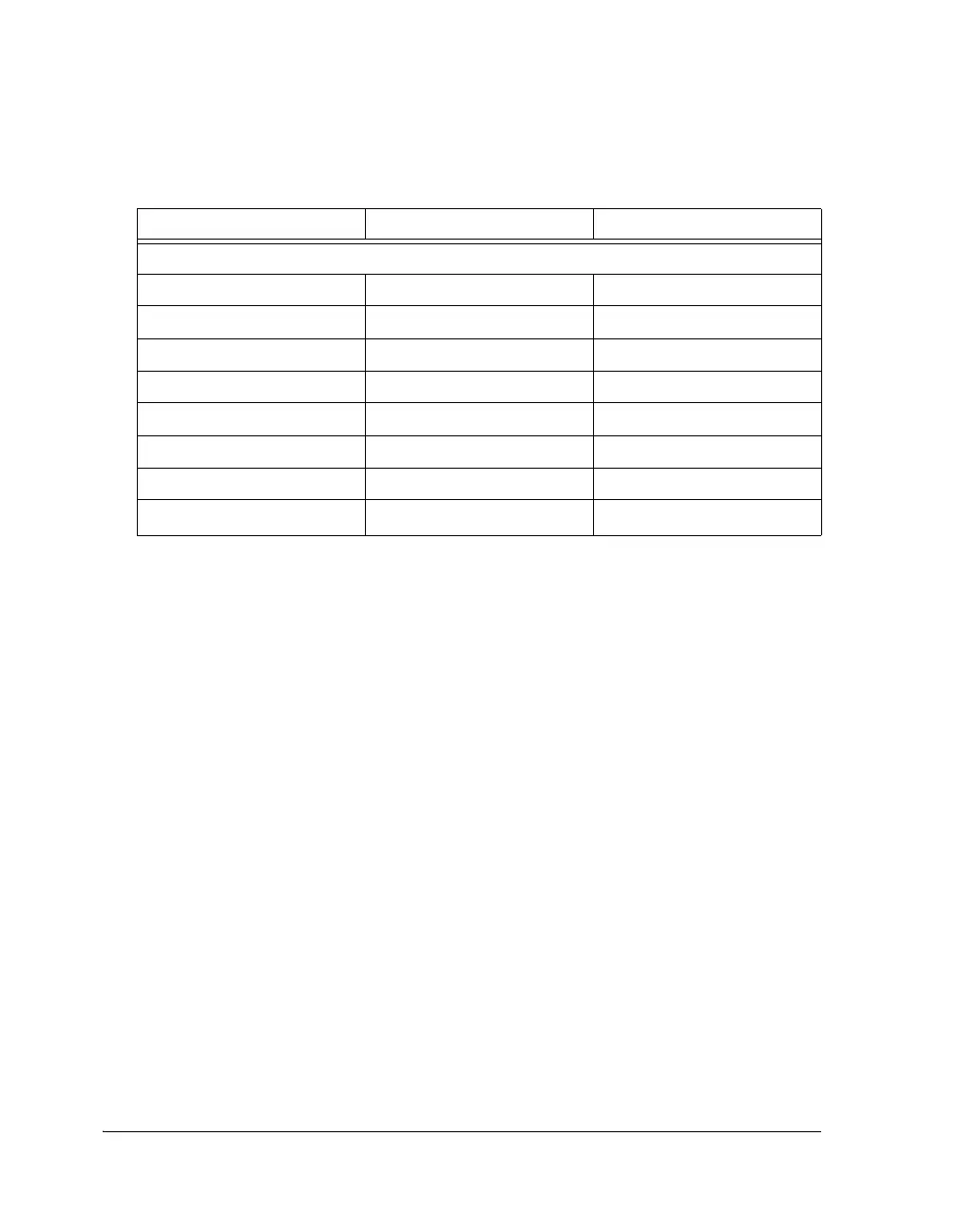

Access Type

Data Buffer No No

Core Data Access N/A N/A

DMA Data Access N/A N/A

DMA Channels N/A N/A

DMA Chaining N/A N/A

Boot Capable N/A N/A

Local Memory No No

Clock Operation f

PCLK

f

PCLK

Table 14-1. PCG Specifications (Cont’d)

Feature PCGA–B PCGC–D

Loading...

Loading...