Programming Model

21-24 ADSP-214xx SHARC Processor Hardware Reference

Repeated Start Condition

In general, a repeated start condition is the absence of a stop condition

between two transfers initiated by the same master. The two transfers can

be of any direction type. Examples include a transmit followed by a

receive, or a receive followed by a transmit. During a repeated start

transfer, each interrupt must be serviced correctly to avoid errors. The fol-

lowing sections are intended to assist the programmer with service routine

development.

Transmit/Receive Repeated Start Sequence

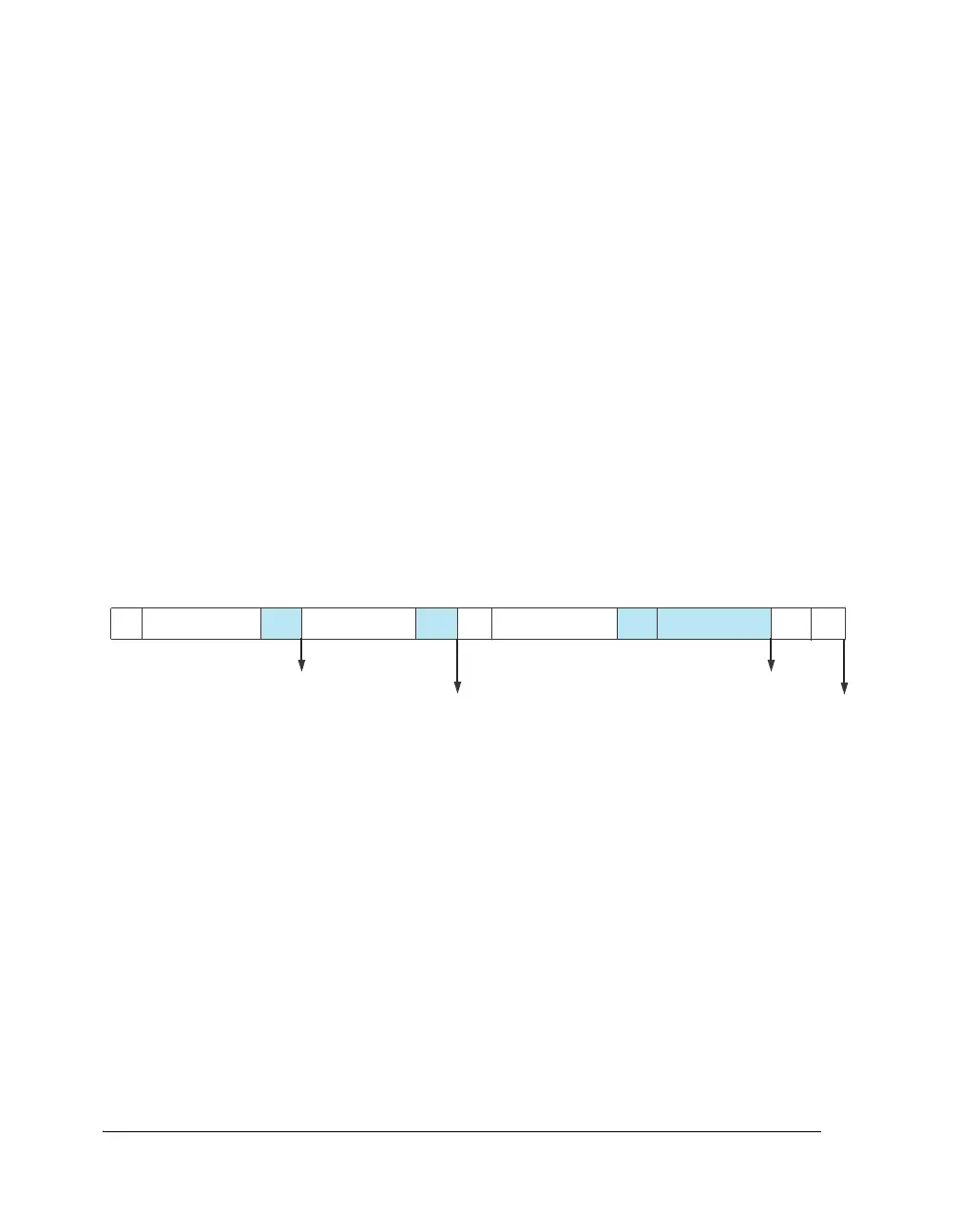

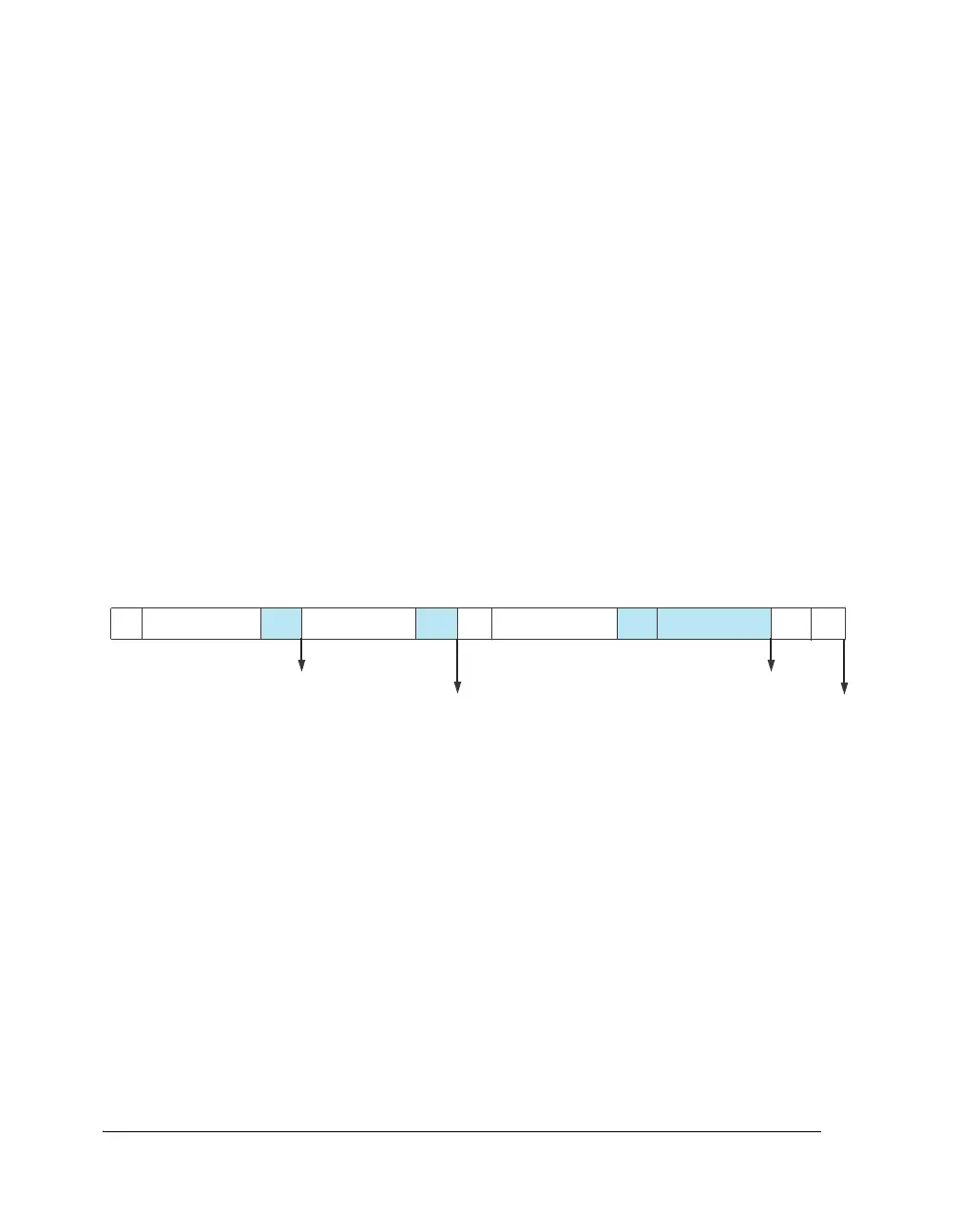

Figure 21-11 illustrates a repeated start data transmit followed by a data

receive sequence.

The tasks performed at each interrupt are:

•

TWITXINT interrupt

This interrupt is generated every time the transmit FIFO has one

or two byte locations available to be written. To service this inter-

rupt, write a byte or word into the transmit FIFO registers (TXTWI8

or

TXTWI16). During one of these interrupts (preferably the first

time), do the following:

Figure 21-11. Transmit/Receive Data Repeated Start

ACKACKSS8-BIT DATA7-BIT ADDRESS ACK P8-BIT DATA ACK7-BIT ADDRESS

MCOMP INTERRUPT

XMTSERV INTERRUPT

RCVSERV INTERRUPT

MCOMP INTERRUPT

Loading...

Loading...