ADSP-214xx SHARC Processor Hardware Reference A-237

Registers Reference

DMA Configuration Registers (SPIDMAC,

SPIDMACB)

These 17-bit SPI registers are used to control DMA transfers and are

shown in Figure A-133 and described in Table A-123.

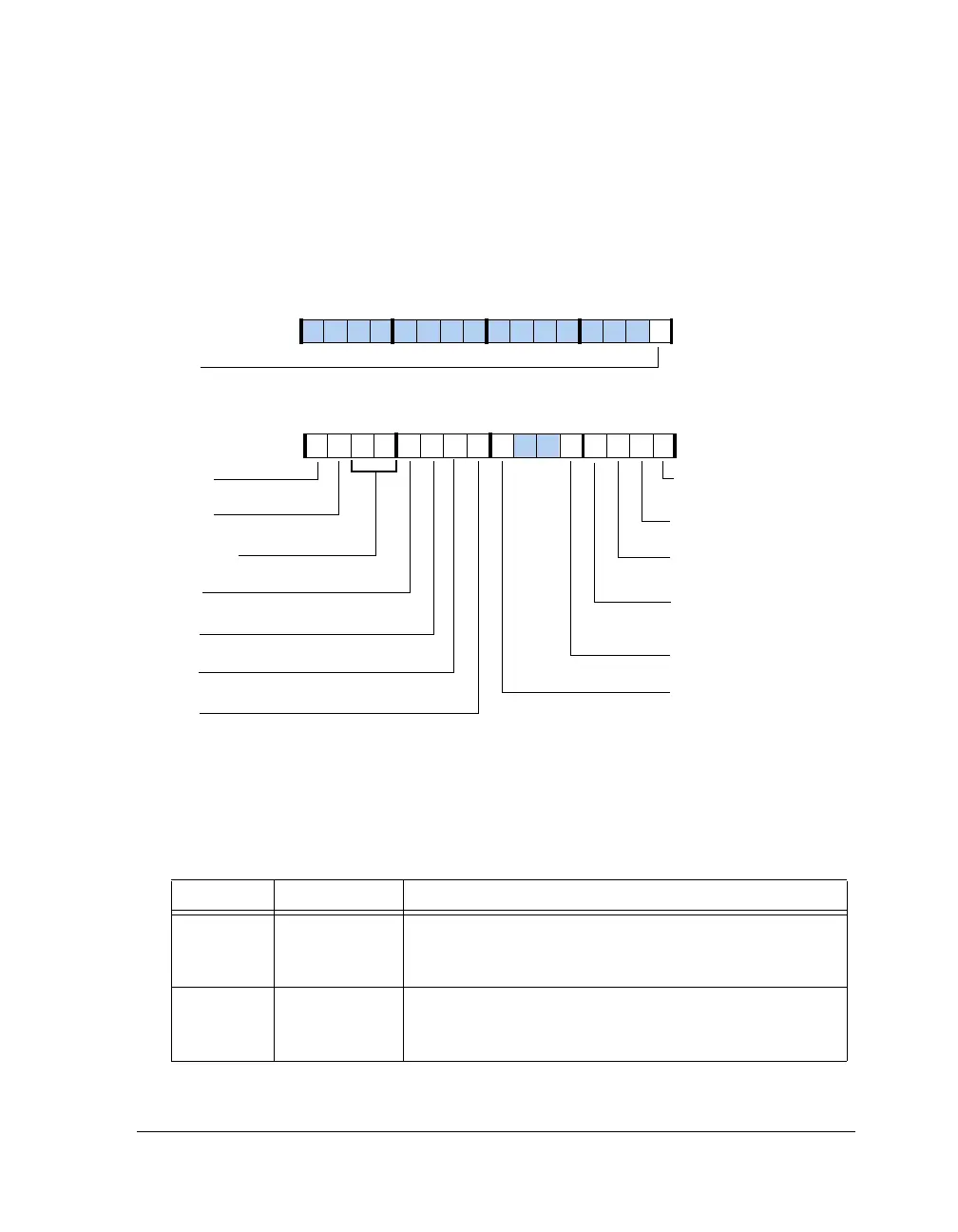

Figure A-133. SPIDMAC, SPIDMACB Registers

Table A-123. SPIDMAC, SPIDMACB Register Bit Descriptions

(RW)

Bit Name Description

0SPIDENDMA Enable.

0 = Disable

1 = Enable

1SPIRCVDMA Write/Read.

0 = SPI transmit (read from internal memory)

1 = SPI receive (write to internal memory)

SPICHS

SPIDEN

SPIDMAS

DMA Transfer Status

DMA Chain Loading Status

SPIERRS

DMA Error Status

SPISx (13–12)

DMA FIFO Status

DMA Enable

SPIRCV

DMA Write/Read

SPIMME

Multimaster Error

SPIUNF

Transmit Underflow Error

Receive Overflow Error

SPIOVF

INTEN

Enable DMA Interrupt on Transfer

DMA FIFO Clear

FIFOFLSH

Enable Interrupt on Error

INTERR

SPI DMA Chaining Enable

SPICHEN

INTETC

Interrupt on External Transfer

Complete Enable

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

Loading...

Loading...