Peripheral Registers

A-78 ADSP-214xx SHARC Processor Hardware Reference

Multiplier Status Register (FFTMACSTAT)

The

FFT_MACSTAT register, described in Table A-44, can be written only in

debug mode. The status bits are sticky and are cleared when read.

DMA Status Register

The bits in the status register, described in Table A-45 report DMA status

information.

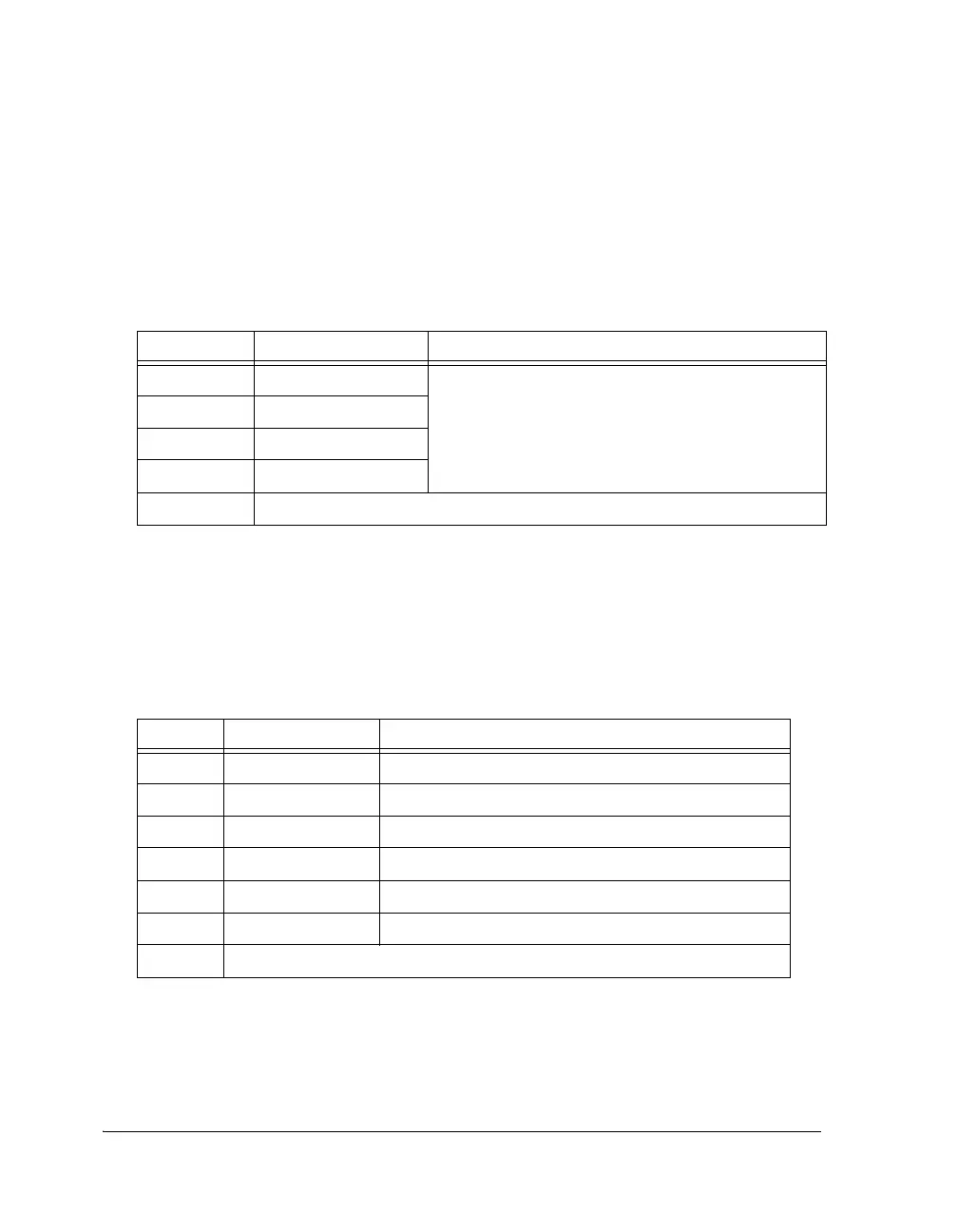

Table A-44. FFT_MACSTAT Register Bit Descriptions (ROC)

Bits Name Description

0FFT_NAN

Bits 3–0 follow the IEEE STD for floating point num-

bers.

1FFT_DENORM

2FFT_OVR

3FFT_UDR

31–4 Reserved

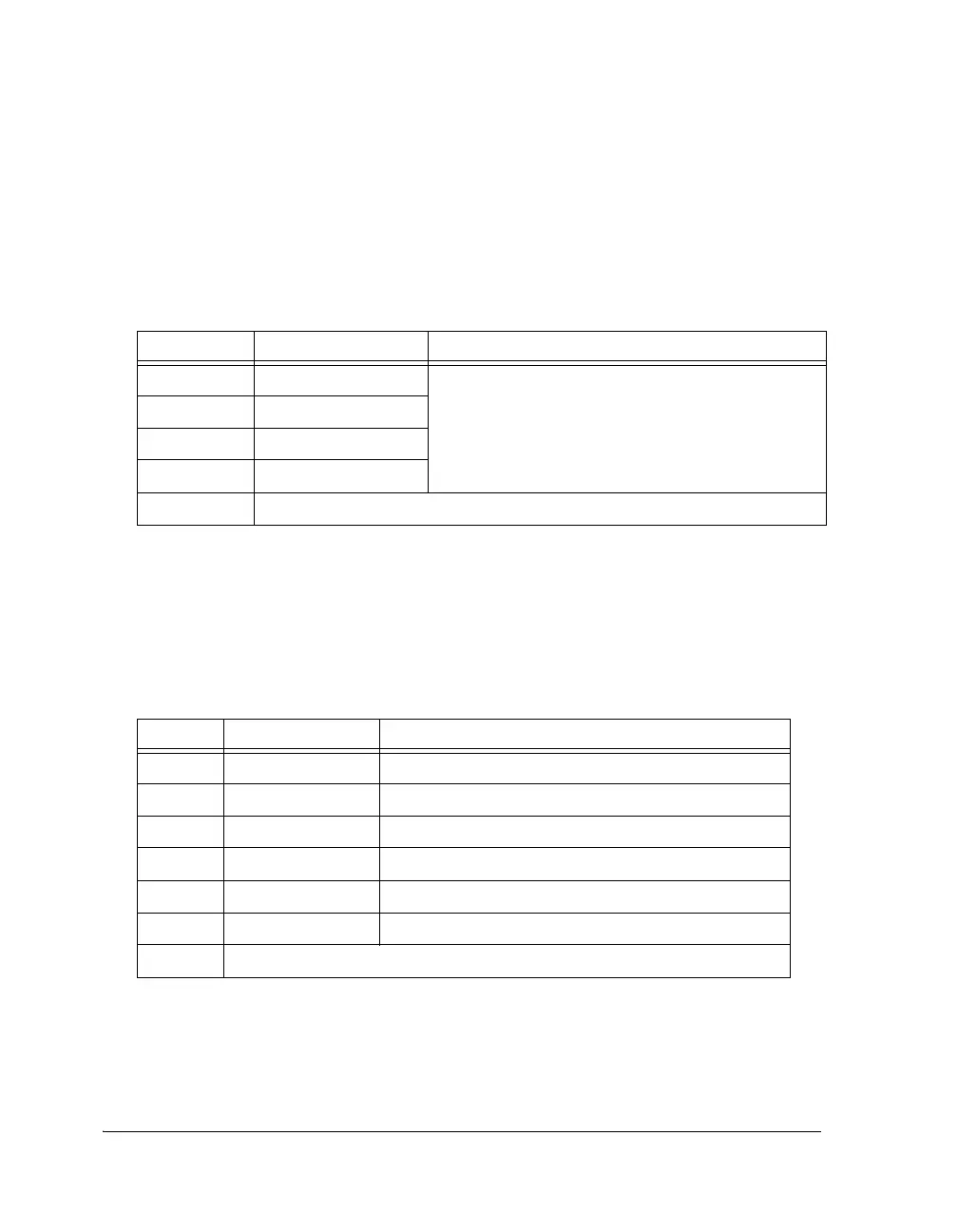

Table A-45. FFTDMASTAT Register Bit Descriptions (RO)

Bits Name Description

0 ICPLD Input Chain Pointer Loading

1 IDMASTAT Input DMA in Progress

2 (ROC) IDMACHIRPT Input DMA Channel Interrupt

3 OCPLD Output Chain Pointer Loading

4 ODMASTAT Output DMA in Progress

5 (ROC) ODMACHIRPT Output DMA Channel Interrupt

31–6 Reserved

Loading...

Loading...