DPI Signal Routing Unit Registers

A-226 ADSP-214xx SHARC Processor Hardware Reference

Pin Enable Signal Routing

(SRU2_PBENx, Group C)

Group C signals, shown in Table A-120, are used to specify whether each

DPI pin is used as an output or an input by setting the source for the pin

buffer enable. When a pin buffer enable (DPI_PBENxx_I) is set (= 1), the

signal present at the corresponding pin buffer input (

DPI_PBxx_I) is driven

off chip as an output. When a pin buffer enable is cleared (= 0), the signal

present at the corresponding pin buffer input is ignored.

The pin enable control registers activate the drive buffer for each of the 14

DPI pins. When the pins are not enabled (driven), they can be used as

inputs.

The registers that control group C settings are shown in Figure A-127

through Figure A-129.

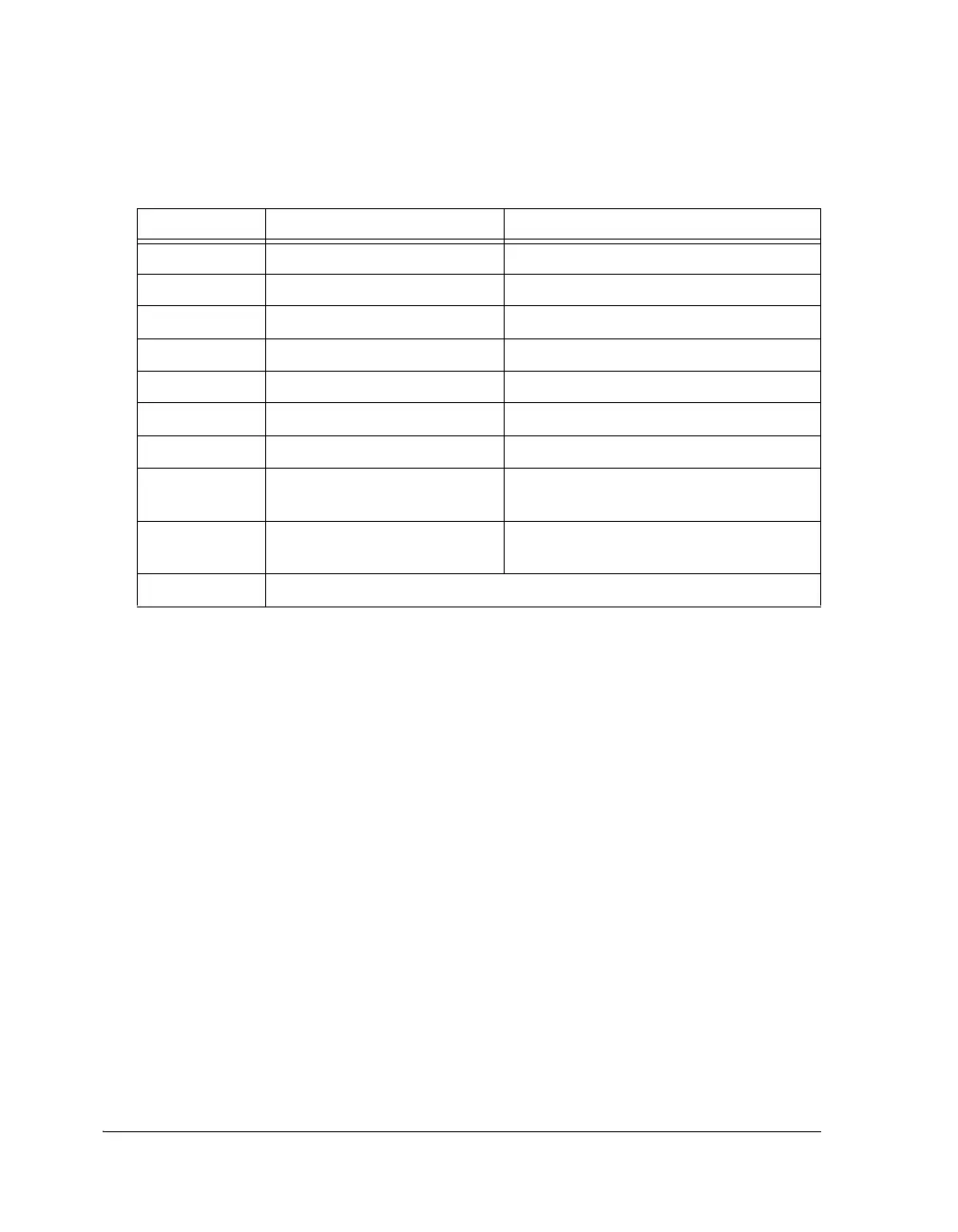

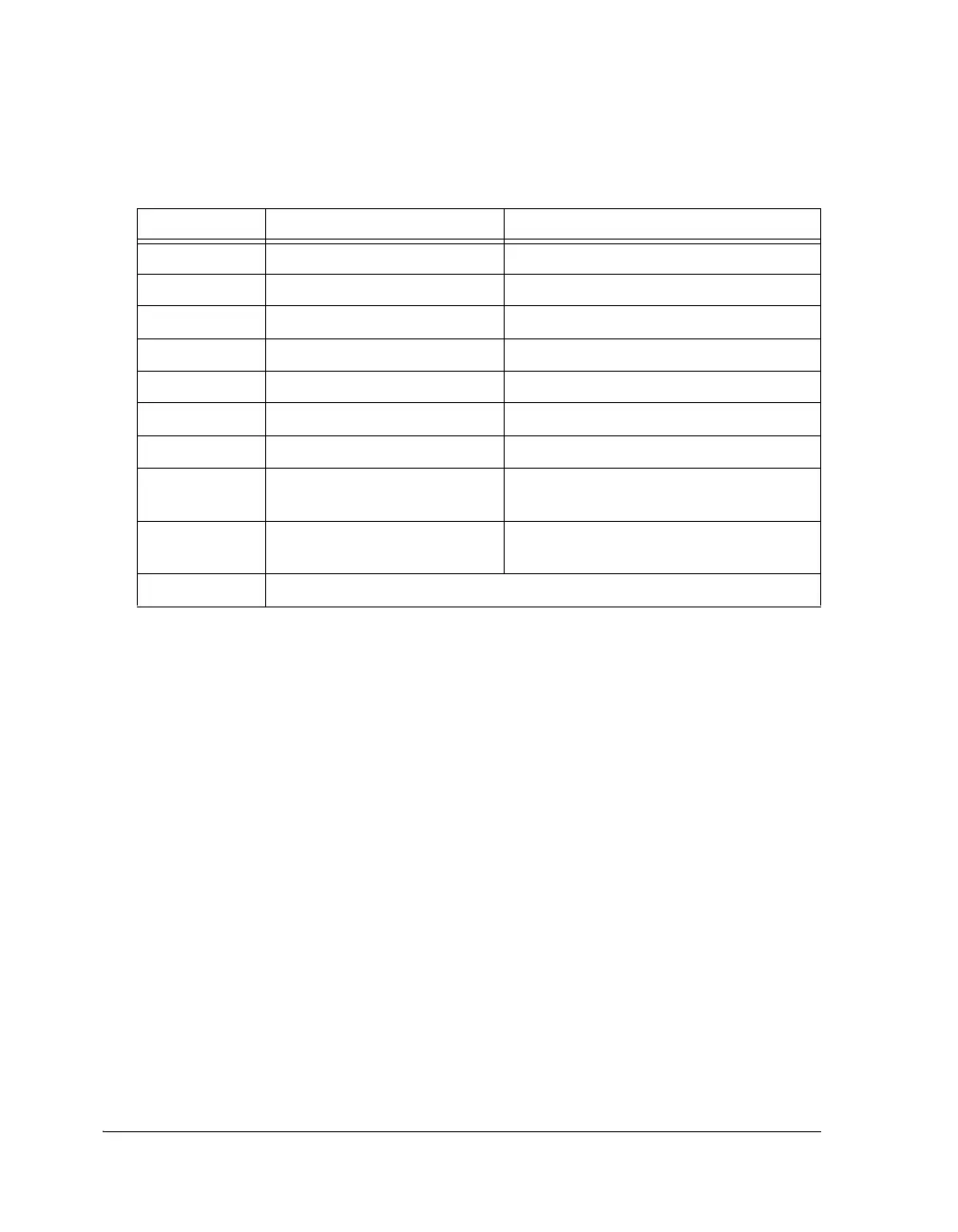

101010 (0x2A) FLAG11_O Flag/PWM 11 Output

101011 (0x2B) FLAG12_O Flag/PWM 12 Output

101100 (0x2C) FLAG13_O Flag/PWM 13 Output

101101 (0x2D) FLAG14_O Flag/PWM 14 Output

101110 (0x2E) FLAG15_O Flag/PWM 15 Output

101111 (0x2F) PCG_CLKC_O Precision Clock Generator Clock C Out

110000 (0x30) PCG_CLKD_O Precision Clock Generator Clock D Out

110001 (0x31) PCG_FSC_O Precision Clock Generator Frame Sync C

Out

110010 (0x32) PCG_FSD_O Precision Clock Generator Frame Sync D

Out

110011–111111 Reserved

1 PWM not available on ADSP-2146x models.

Table A-119. Group B Signals (Cont’d)

Binary Signal Description (Source Selection)

Loading...

Loading...