ADSP-214xx SHARC Processor Hardware Reference A-75

Registers Reference

General Control Register (FFTCTL1)

The global control register (

FFTCTL1) shown in Figure A-33 and described

in Table A-41 is used to enable, start, and reset the FFT module. It is also

used to enable DMA and debug operation.

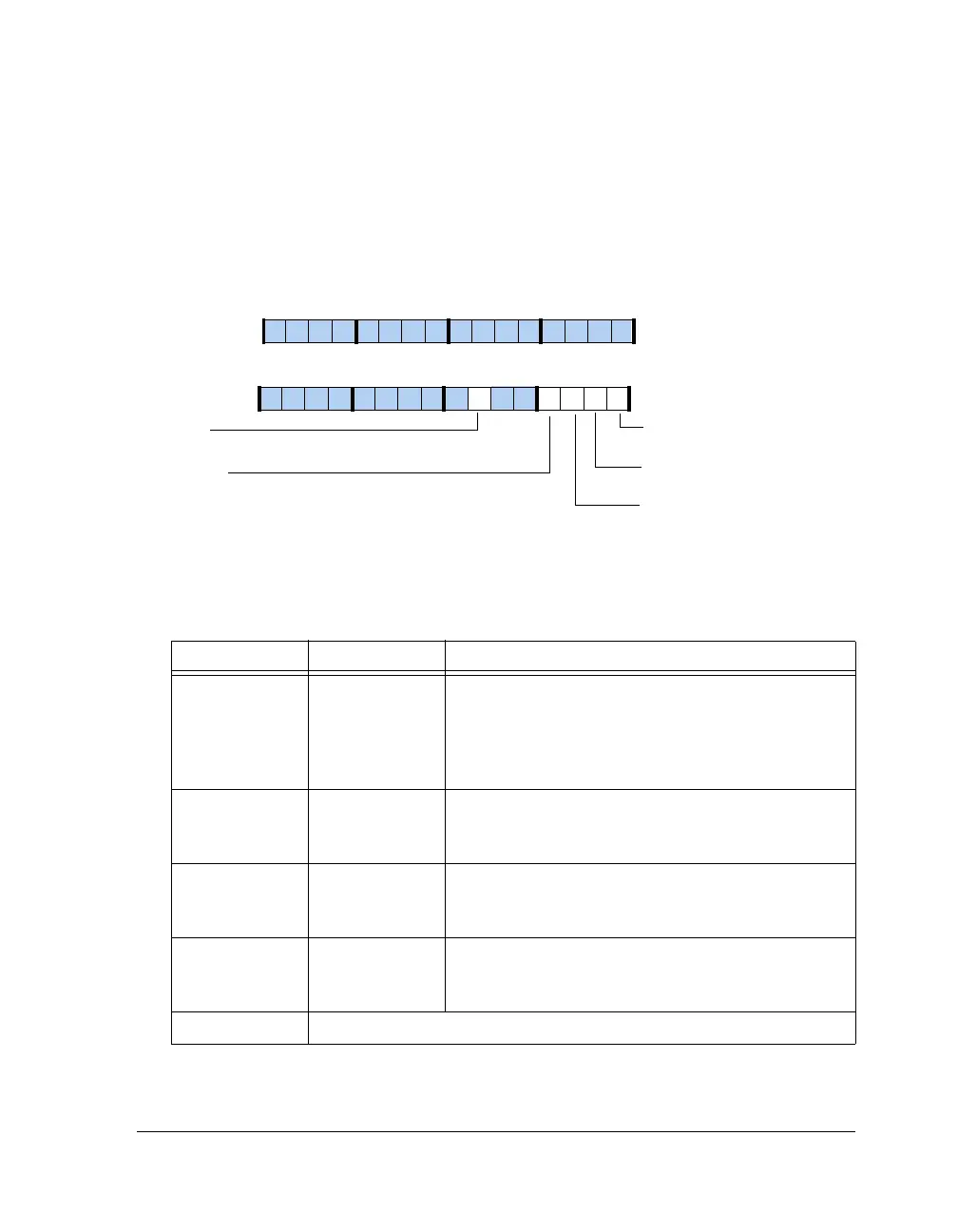

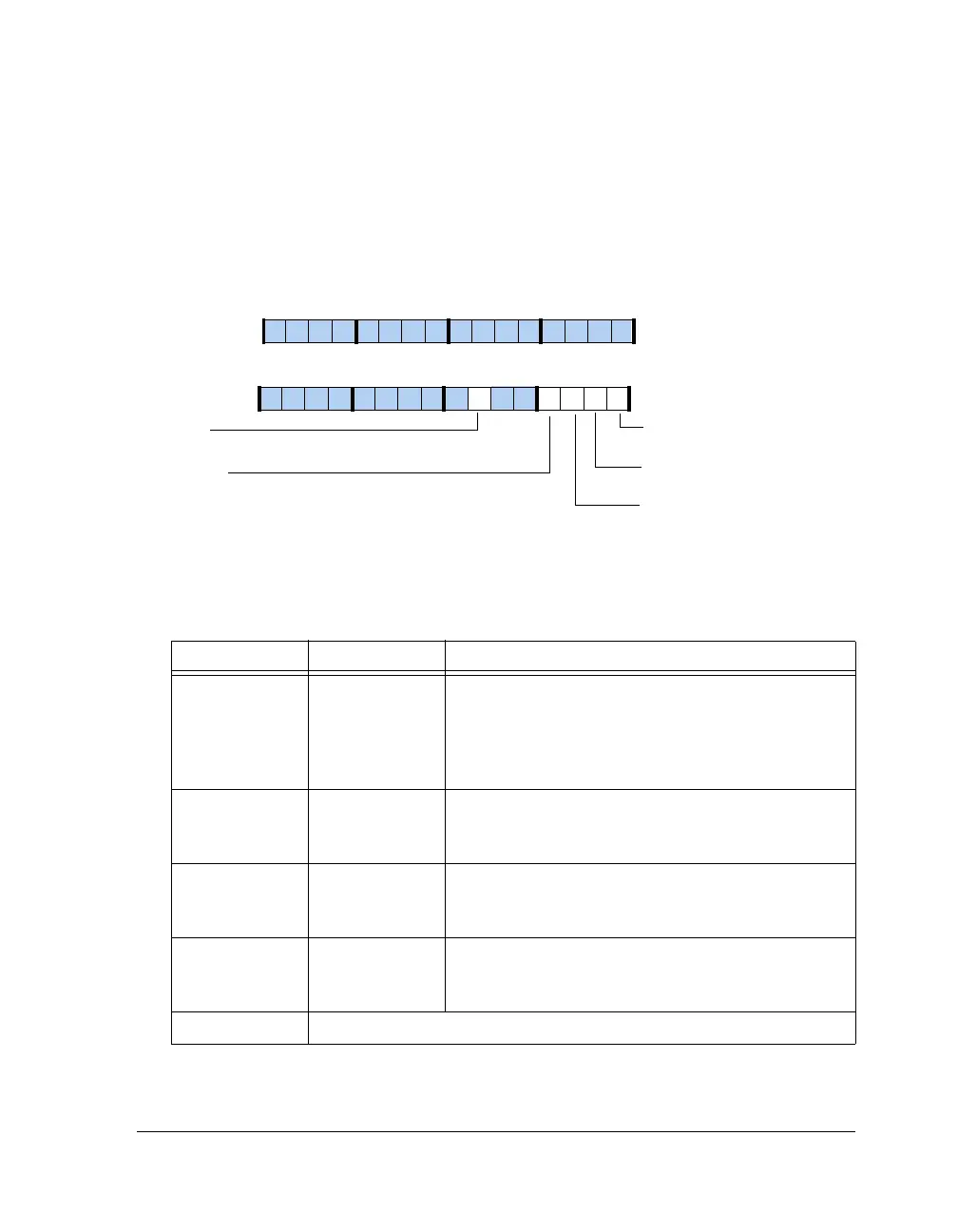

Figure A-33. FFTCTL1 Register

Table A-42. FFTCTL1 Register Bit Descriptions (RW)

Bits Name Description

0 FFT_RST Reset Accelerator. Setting this bit puts the accelerator

into reset mode. Explicit clearing of this bit is necessary

to take the accelerator out of reset.

0 = Normal operation

1 = Reset

1 FFT_EN Accelerator Enable.

0 = Disable

1 = Enable

2 FFT_START Start Accelerator.

0 = Idle

1 = Start

3 FFT_DMAEN DMA Enable.

0 = Disable

1 = Enable

5–4 Reserved

FFT_DBG

Debug Mode Enable

FFT_RST

FFT_EN

Accelerator Enable

Accelerator Reset

FFT_START

Accelerator Start

FFT_DMAEN

DMA Enable

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

Loading...

Loading...