TDM Mode

C-8 ADSP-214xx SHARC Processor Hardware Reference

MOST Mode

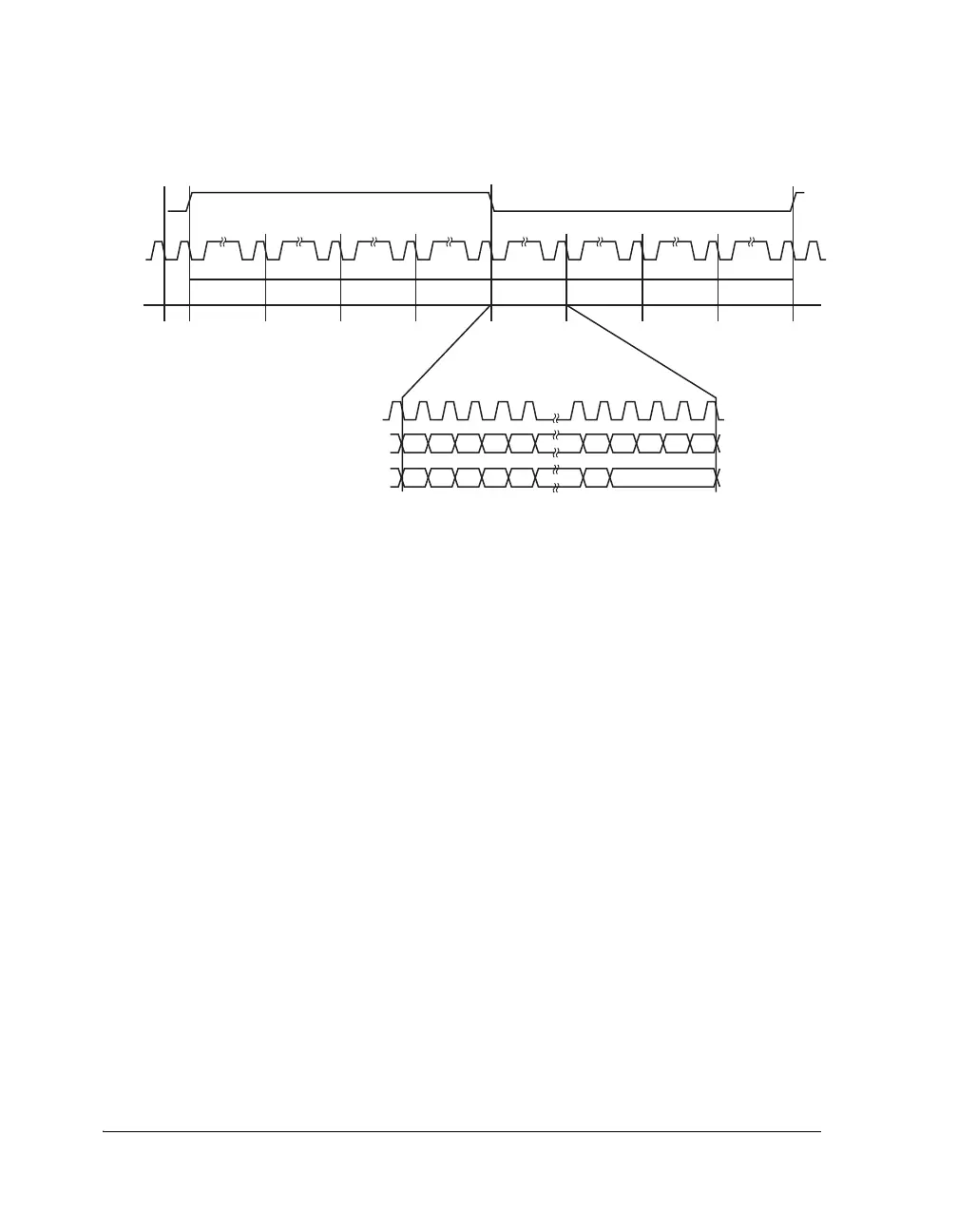

A special packed TDM mode is available that allows four channels to be

fit into a space of 64-bit clock cycles. This mode is called packed TDM4

mode, or MOST™ mode. MOST (Media Oriented Systems Transport) is

a networking standard intended for interconnecting multimedia compo-

nents in automobiles and other vehicles. Many integrated circuits

intended to interface with a MOST bus use a packed TDM4 data format.

Figure C-3 illustrates a word length of 16 bits for a timing diagram of the

packed TDM4 mode. This figure is shown with a negative BCLK polarity, a

negative LRCLK polarity, and an MSB delay of 1. The MSB position of the

serial data must be delayed by one bit clock from the start of the frame

(I

2

S position).

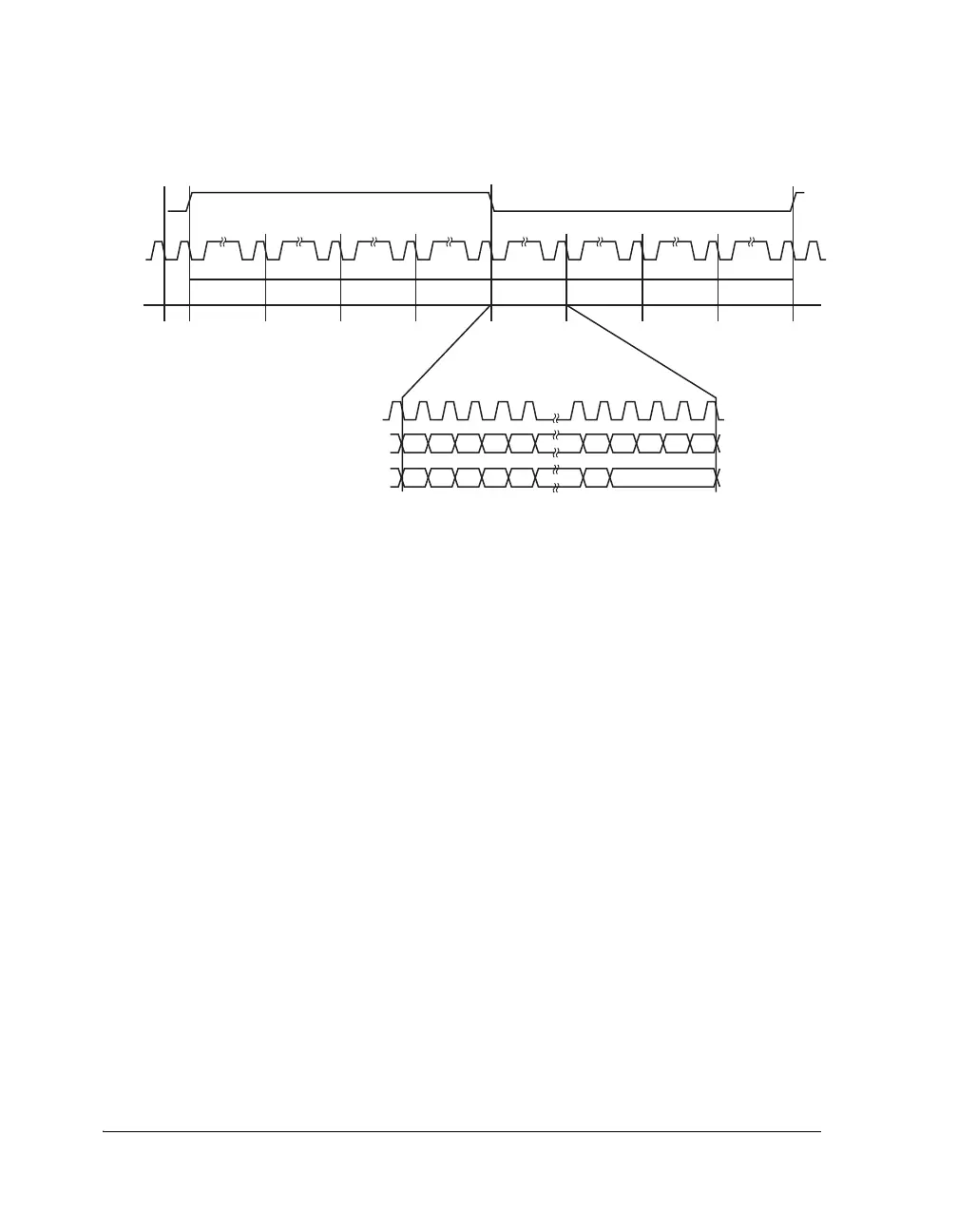

Figure C-2. Packed I2S Mode

SLOT 1

LEFT 0

SLOT 2

LEFT 1

SLOT 3

LEFT 2

BLANK SLOT

4 SCLK

SLOT 4

RIGHT 0

SLOT 5

RIGHT 1

SLOT 6

RIGHT 2

BLANK SLOT

4 SCLK

DATA

20-BIT DATA

16-BIT DATA

BCLK

BCLK

MSB

–1

MSB

–2

MSB

–3

MSB

–4

MSB

–1

MSB

–2

MSB

–3

MSB

–4

LSB

+4

LSB

+3

LSB

+2

LSB

+1

MSB LSB

LSBMSB

L/RCLK

Loading...

Loading...