Interrupt Priority

B-8 ADSP-214xx SHARC Processor Hardware Reference

Priority Interrupt Control Registers (PICRx)

This 32-bit read/write registers, shown in Figure B-1 through Figure B-4,

control programmable priority interrupts and default interrupt sources.

An example is shown below.

Route PWMI to P17I

#include <def21469.h>

ustat1=dm(PICR2);

bit set ustat1 P17I4|P17I3; /*PWMI 0x18, I4-0= 11000*/

bit clr ustat1 P17I2|P17I1|P17I0;

dm(PICR2)=ustat1;

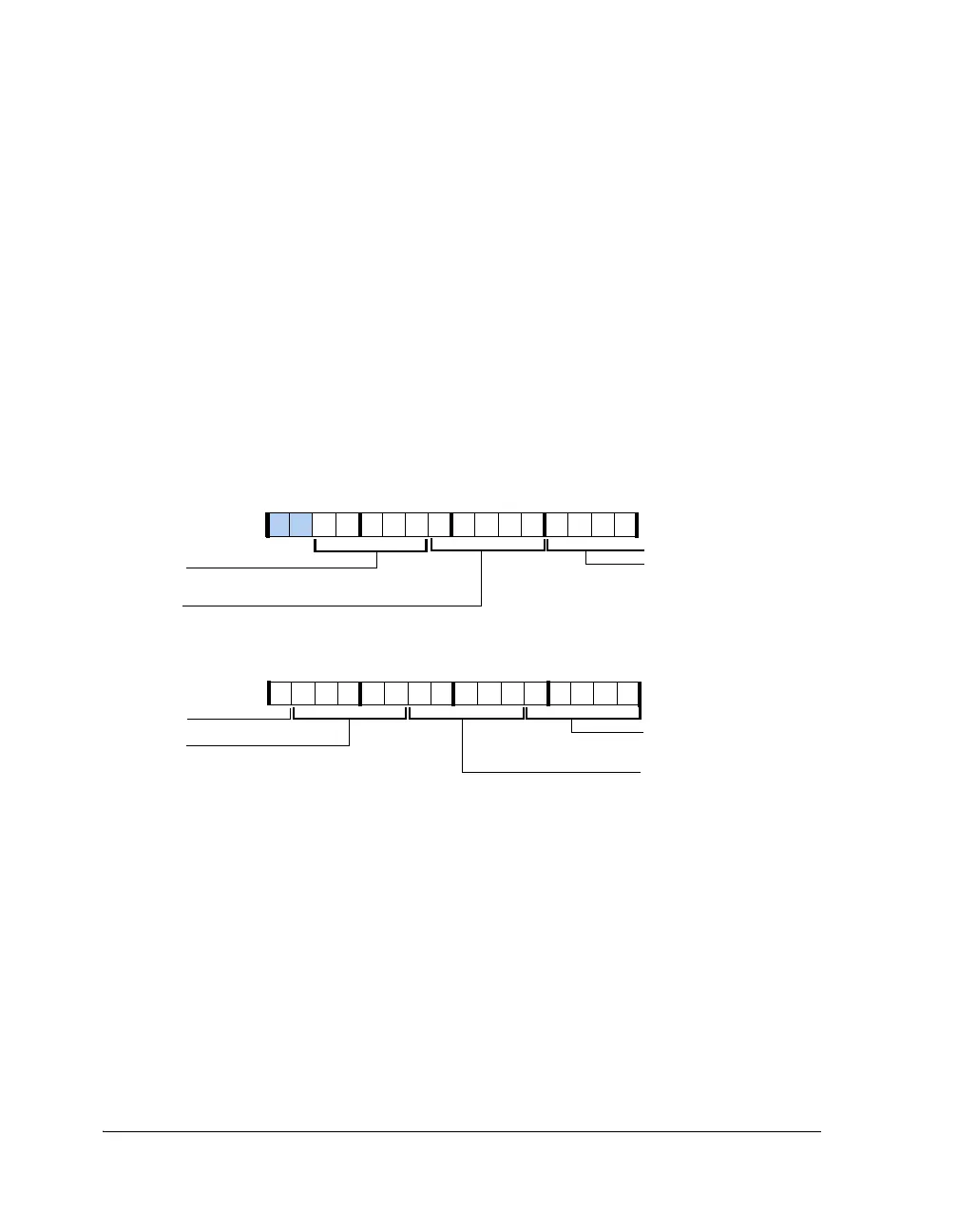

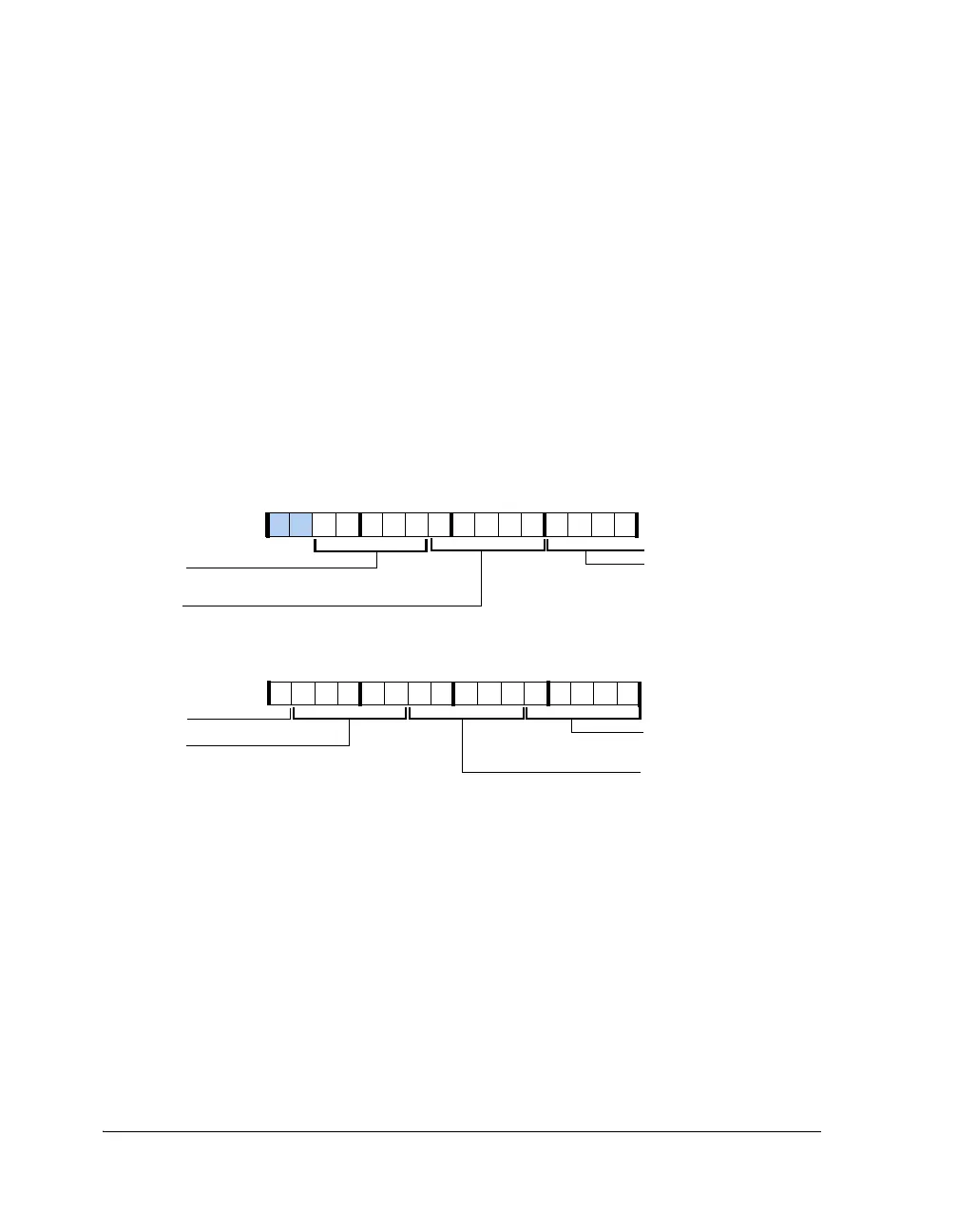

Figure B-1. PICR0 Register

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

00000000000 00000

15 14 13 12 11 10 9 8 76 54 3 210

000000000 00 00000

P5I (29–25)

Programmable Interrupt 1

P1I (9–5)

Programmable Interrupt 5

P4I (24–20)

Programmable Interrupt 4

P3I (19–15)

Programmable Interrupt 3

Programmable interrupt 0

P0I (4–0)

programmable interrupt 2

P2I (14–10)

P3I (19–15)

Loading...

Loading...