ADSP-214xx SHARC Processor Hardware Reference A-239

Registers Reference

Baud Rate Registers (SPIBAUD, SPIBAUDB)

These SPI registers are used to set the bit transfer rate for a master device.

When configured as slaves, the value written to these registers is ignored.

The (

SPIBAUDx) registers can be read from or written to at any time. Bit

descriptions are provided in Table A-124. Note that the minimum value

of BAUDR = 0x2, since the max SPICLK = PCLK/4 in master mode.

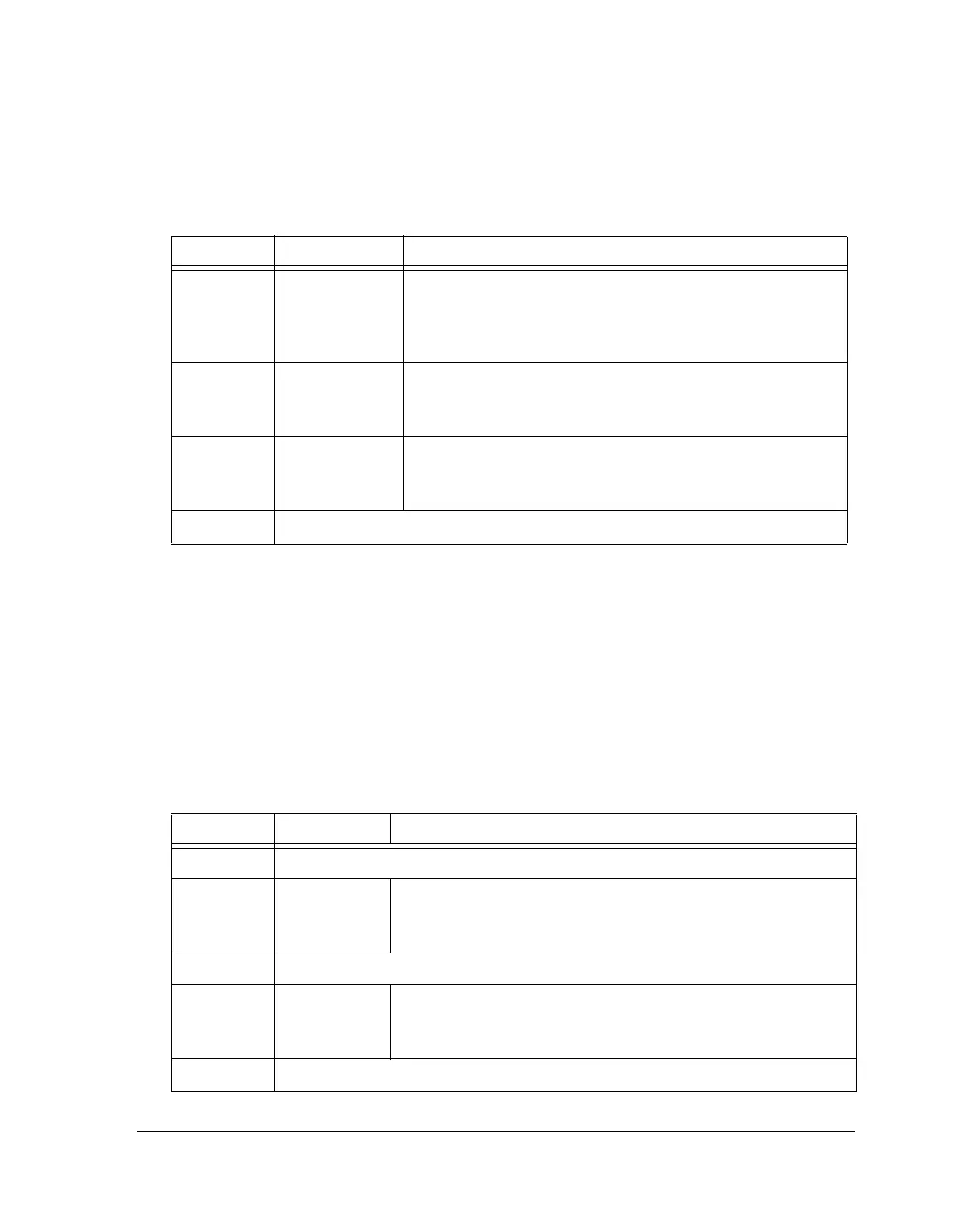

14 (RO) SPIERRS DMA Error Status. This bit is set if SPIOVF, SPIUNF or

DPIMME bits are set.

0 = Successful DMA transfer

1 = Errors during DMA transfer

15 (RO) SPIDMAS DMA Transfer Status.

0 = DMA idle

1 = DMA in progress

16 (RO) SPICHS DMA Chain Loading Status.

0 = Chain idle

1 = Chain loading in progress

31–17 Reserved

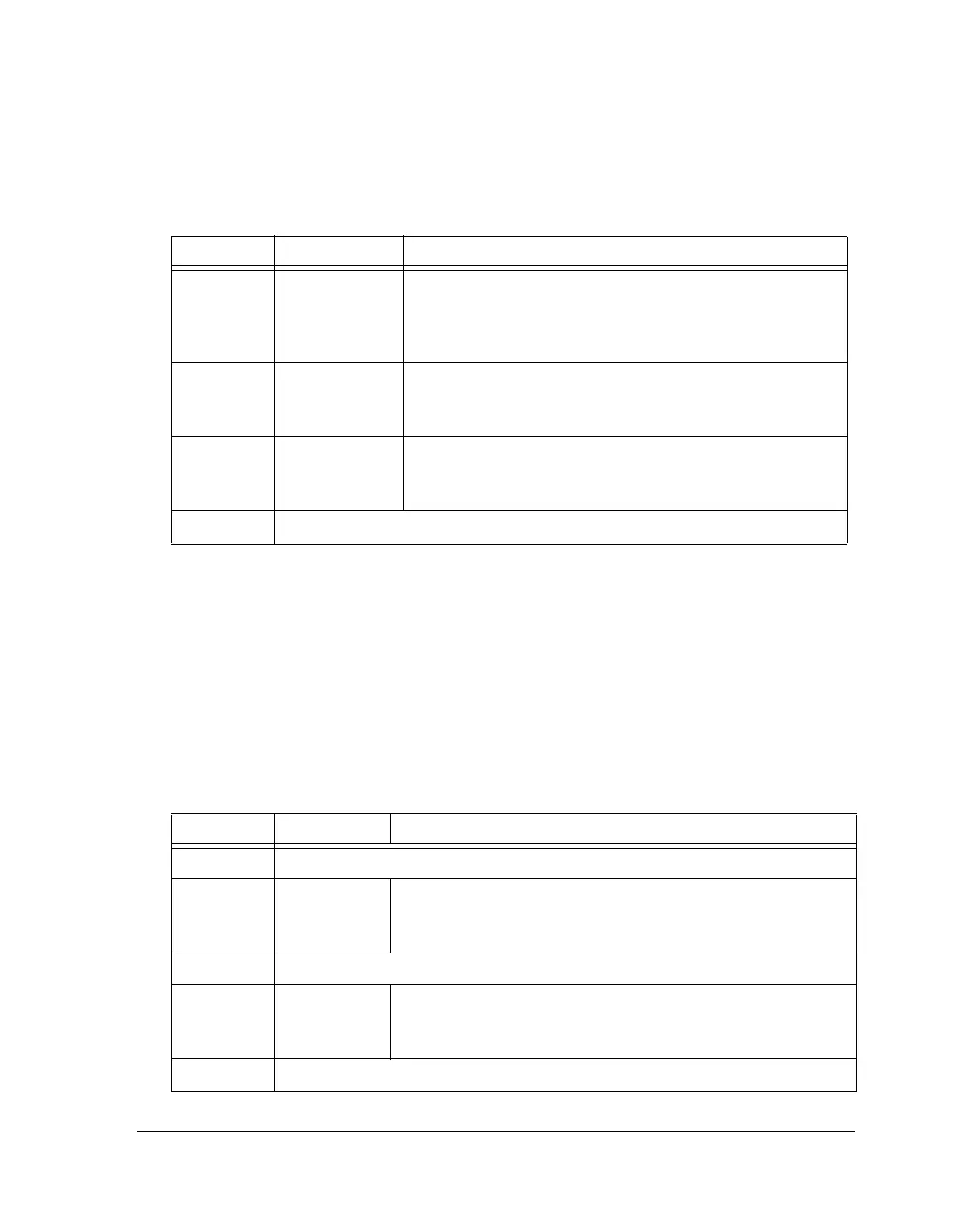

Table A-124. SPIBAUD, SPIBAUDB Register Bit Descriptions (RW)

Bit Name Description

0 Reserved

15–1 BAUDR Baud Rate Enable. Enables the SPICLK per the equation:

SPICLK baud rate = PCLK /(4 x BAUDR)

Default = 0

19–16 Reserved

25–20 STDC Sequential Transfer Delay. The word to word delay(T4) = 1.5 SPI

CLK Period + T3 and T3 = 0.5 SPICLK period for STDC = 0.

T3 = STDC × SPICLK period for STDC > 0.

31–26 Reserved

Table A-123. SPIDMAC, SPIDMACB Register Bit Descriptions

(RW) (Cont’d)

Bit Name Description

Loading...

Loading...