ADSP-214xx SHARC Processor Hardware Reference 23-17

System Design

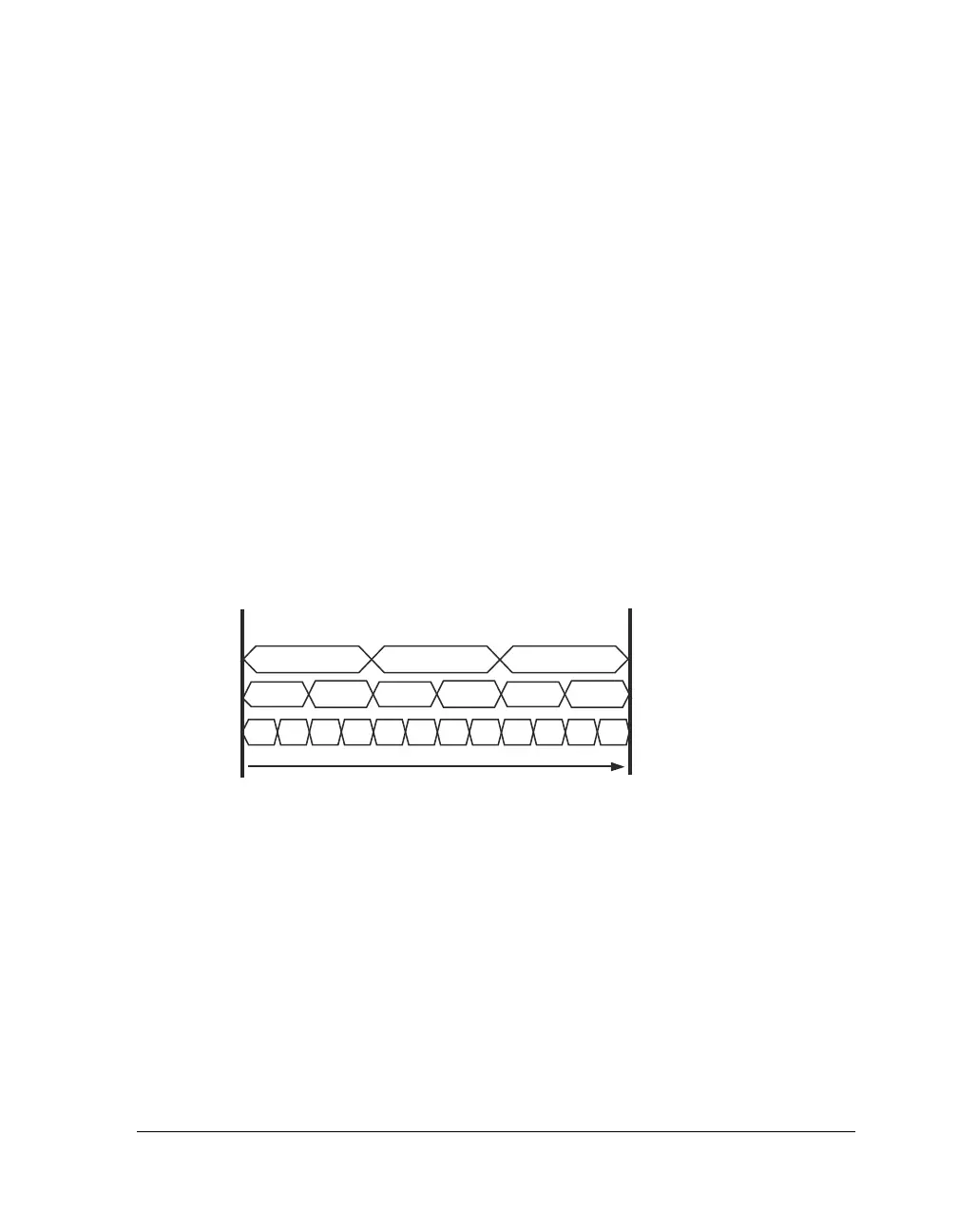

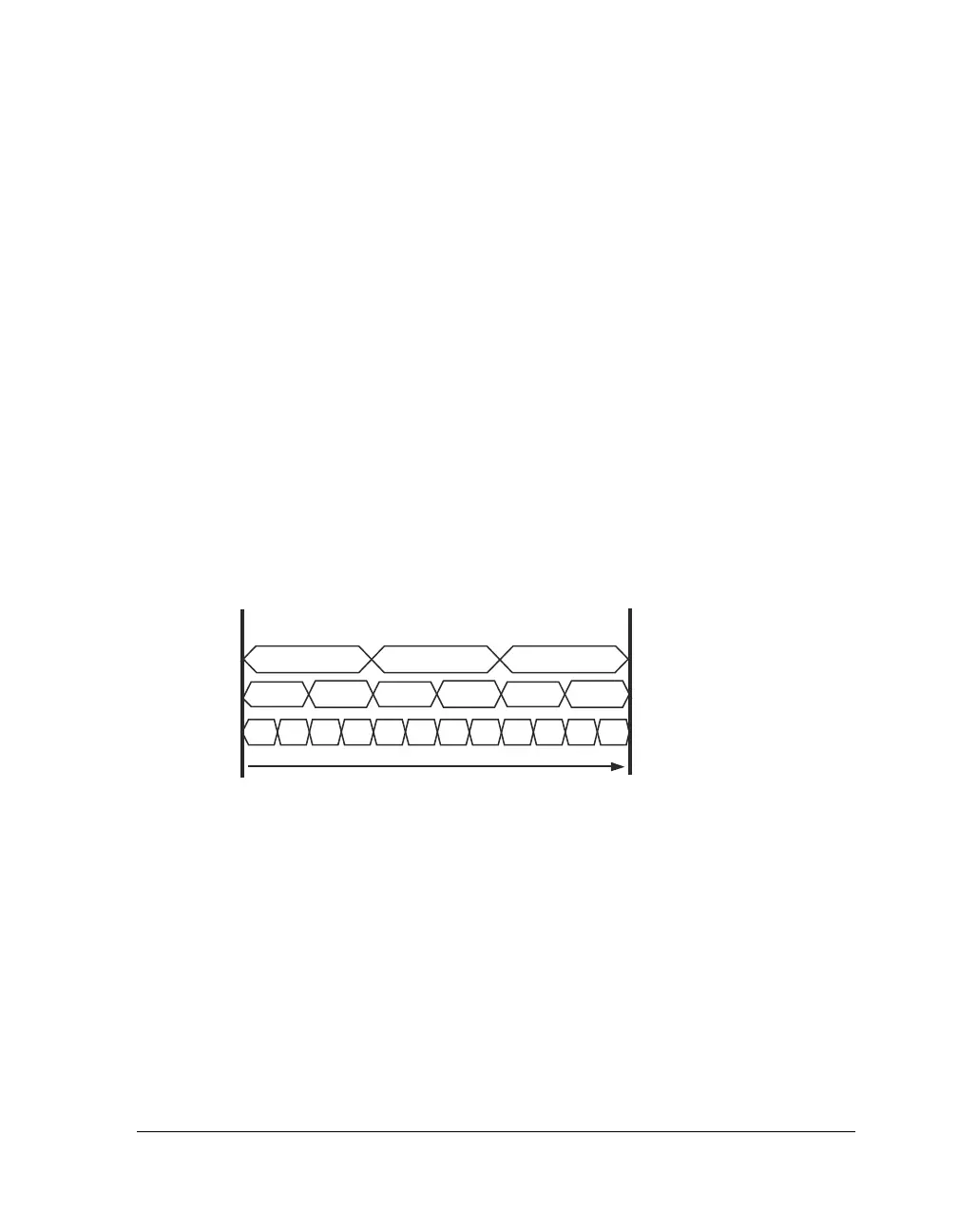

SPI Boot Packing

In all SPI boot modes, the data word size in the shift register is hardwired

to 32 bits. Therefore, for 8- or 16-bit devices, data words are packed into

the shift register to generate 32-bit words least significant bit (LSB) first,

which are then shifted into internal memory. The relationship between

the 32-bit words received into the

RXSPI register and the instructions that

need to be placed in internal memory is shown in the following sections.

For more information about 32- and 48-bit internal memory addressing,

see the “Memory” chapter in the SHARC Processor Programming Reference.

As shown in Figure 23-5, two words shift into the 32-bit receive shift reg-

ister (RXSR) before a DMA transfer to internal memory occurs for 16-bit

SPI devices. For 8-bit SPI devices, four words shift into the 32-bit receive

shift register before a DMA transfer to internal memory occurs.

When booting, the processors expect to receive words into the

RXSPI regis-

ter seamlessly. This means that bits are received continuously without

breaks. For more information, see “Core Transfers” on page 15-20. For

different SPI host sizes, the processor expects to receive instructions and

data packed in a least significant word (LSW) format.

Figure 23-5. Instruction Packing for Different Hosts

16-BIT HOST

CCDD1122

1122

33445566 7788AABB

CCDD AABB 778833445566

66 55 44 33 22 11 DD CC BB AA 88 77

32-BIT HOST

8-BIT HOST

[0x8C000] 0x1122 33445566

[0x8C001] 0x7788 AABBCCDD

WORDS

INSTRUCTIONS IN

INTERNAL MEMORY

t=0 t=96 SPICLK

Loading...

Loading...