Processor Booting

23-16 ADSP-214xx SHARC Processor Hardware Reference

Since the SPI host initiates the transfers, a handshake between master and

slave is required for synchronization. One possible solution is to use the

slave’s

SPI_MISO_O signal as handshake signal. If a pause is required, the

slave transmits zeros or ones to the master. Another solution is to connect

this signal to the master’s flag input to generate an interrupt for the same

purpose.

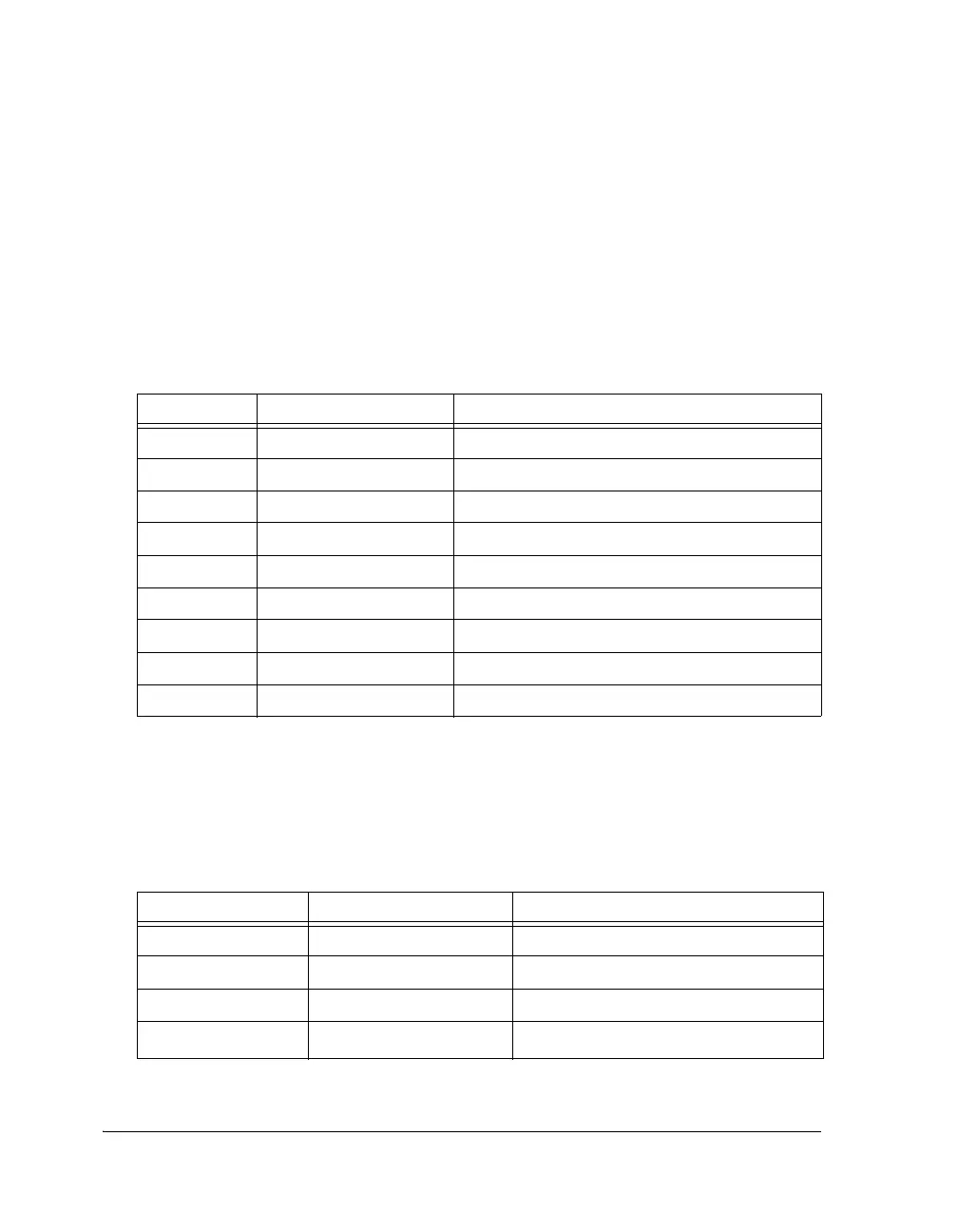

The SPI DMA channel is used when downloading the boot kernel infor-

mation to the processor. At reset, the DMA parameter registers are

initialized to the values listed in Table 23-10.

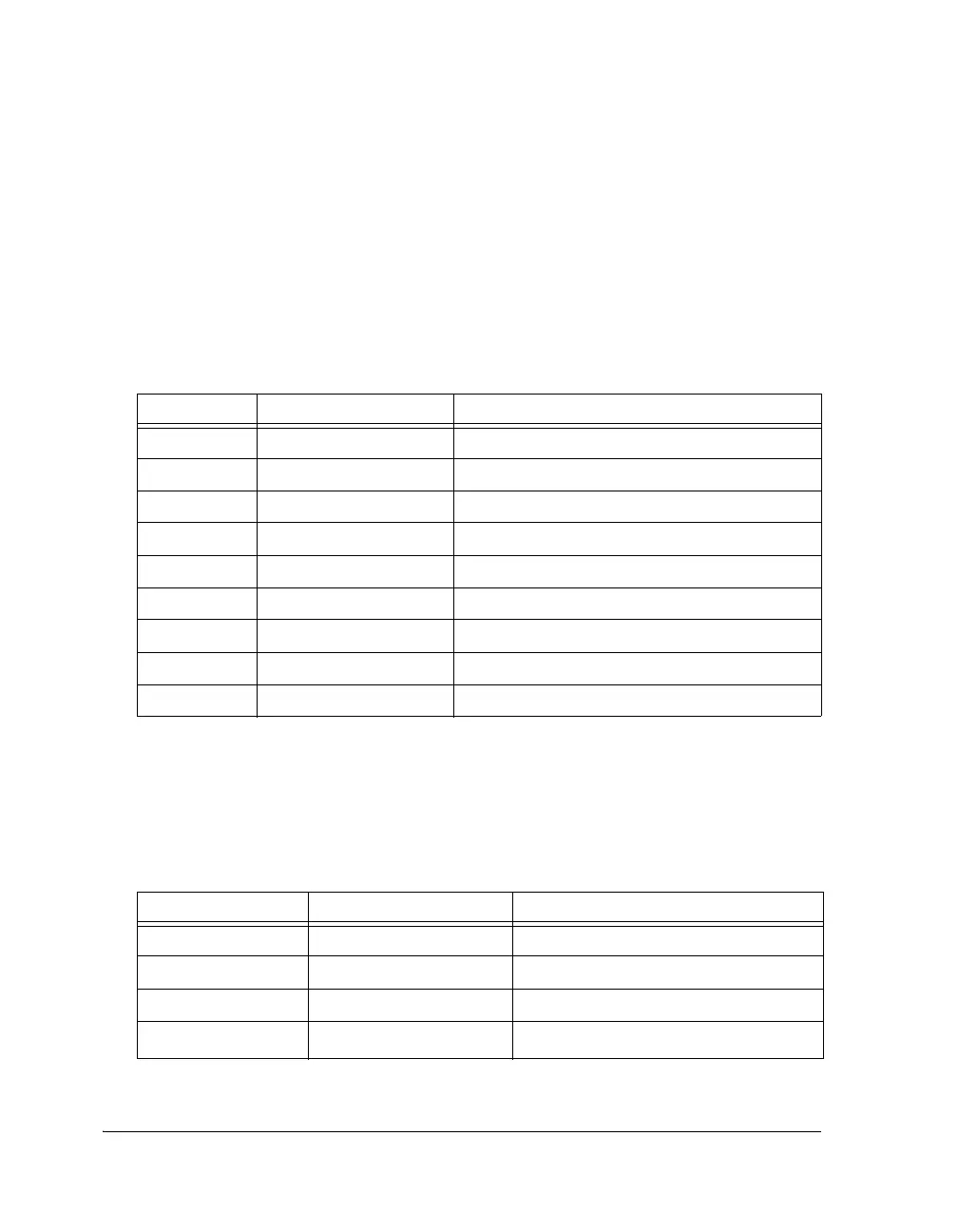

Table 23-9. SPICTL Slave Boot Settings (0x4D22)

Bit Setting Comment

SPIEN Set (= 1) SPI enabled

SPIMS Cleared (= 0) Slave device

MSBF Cleared (= 0) LSB first

WL 10, 32-bit SPI Receive shift register word length

DMISO Set (= 1) MISO MISO disabled

SENDZ Cleared (= 0) Send last word

SPIRCV Set (= 1) Receive DMA enabled

CLKPL Set (= 1) Active low SPI clock

CPHASE Set (= 1) Toggle SPICLK at the beginning of the first bit

Table 23-10. Parameter Initialization for SPI Slave Boot

Parameter Register Initialization Value Comment

SPIDMAC 0x0000 0007 Enable receive, interrupt on completion

IISPI IVT_START_ADDR Start of block 0

IMSPI 0x1 32-bit data transfers

CSPI 0x180

384

× 32-bit transfers

Loading...

Loading...