Asynchronous Memory Interface

3-16 ADSP-214xx SHARC Processor Hardware Reference

When

ACK is enabled (ACKEN = 1), the processor samples the ACK signal

after two wait states plus the expiration of the wait state count pro-

grammed in the AMICTLx register. It is imperative that the WS value is

initialized when the acknowledge enable bit (ACKEN) is set.

Predictive Reads

The AMI controller allows two types of read access:

• predictive reads (default)

• non predictive reads

Predictive read (PREDIS bit = 0) reduces the time delay between two reads.

The predictive address is generated and compared with the actual address.

If they do not match, then that read data is ignored. Every last read access

is therefore a duplication of the 2nd to last read with the same address.

Note that this redundant read does not update the memory location.

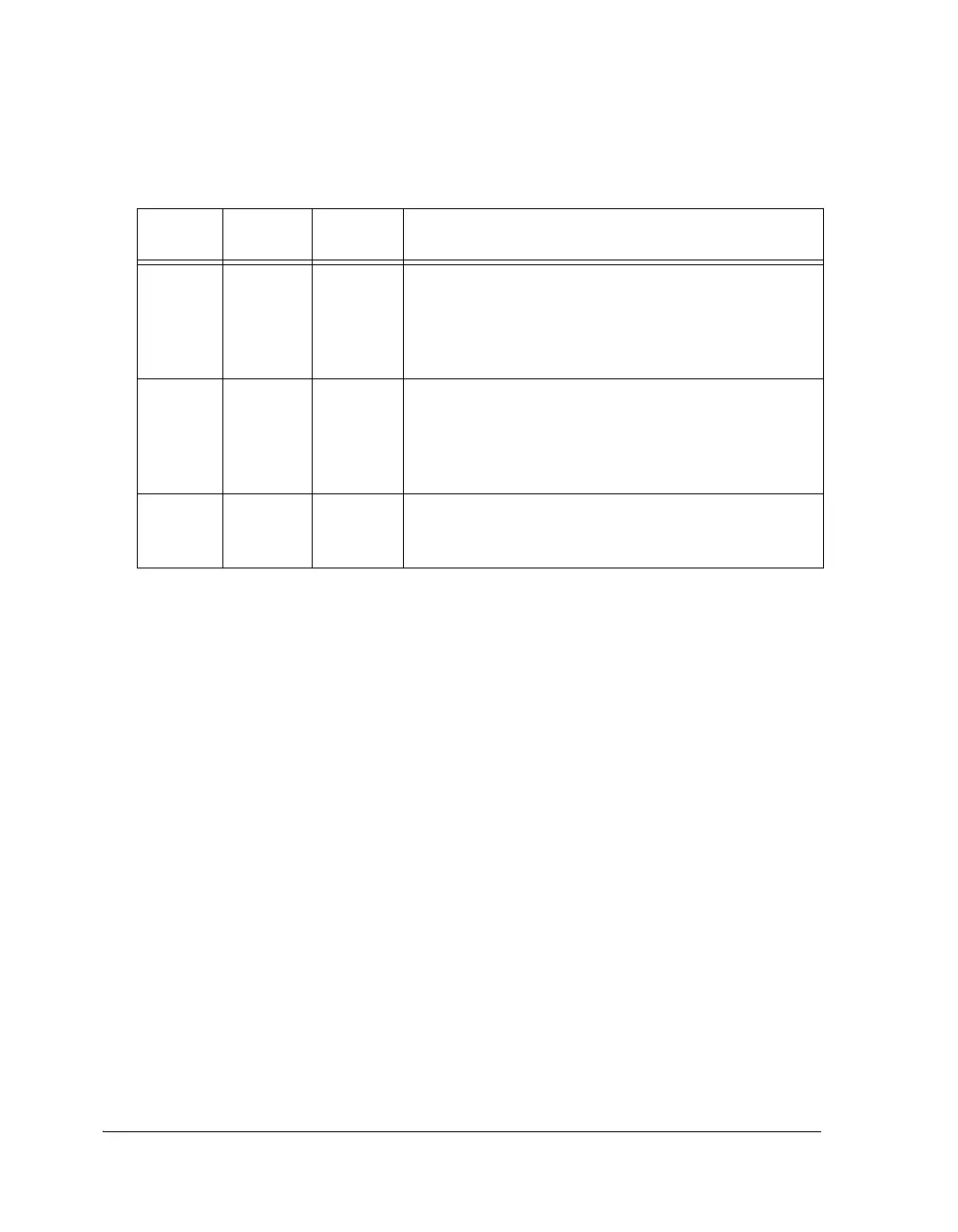

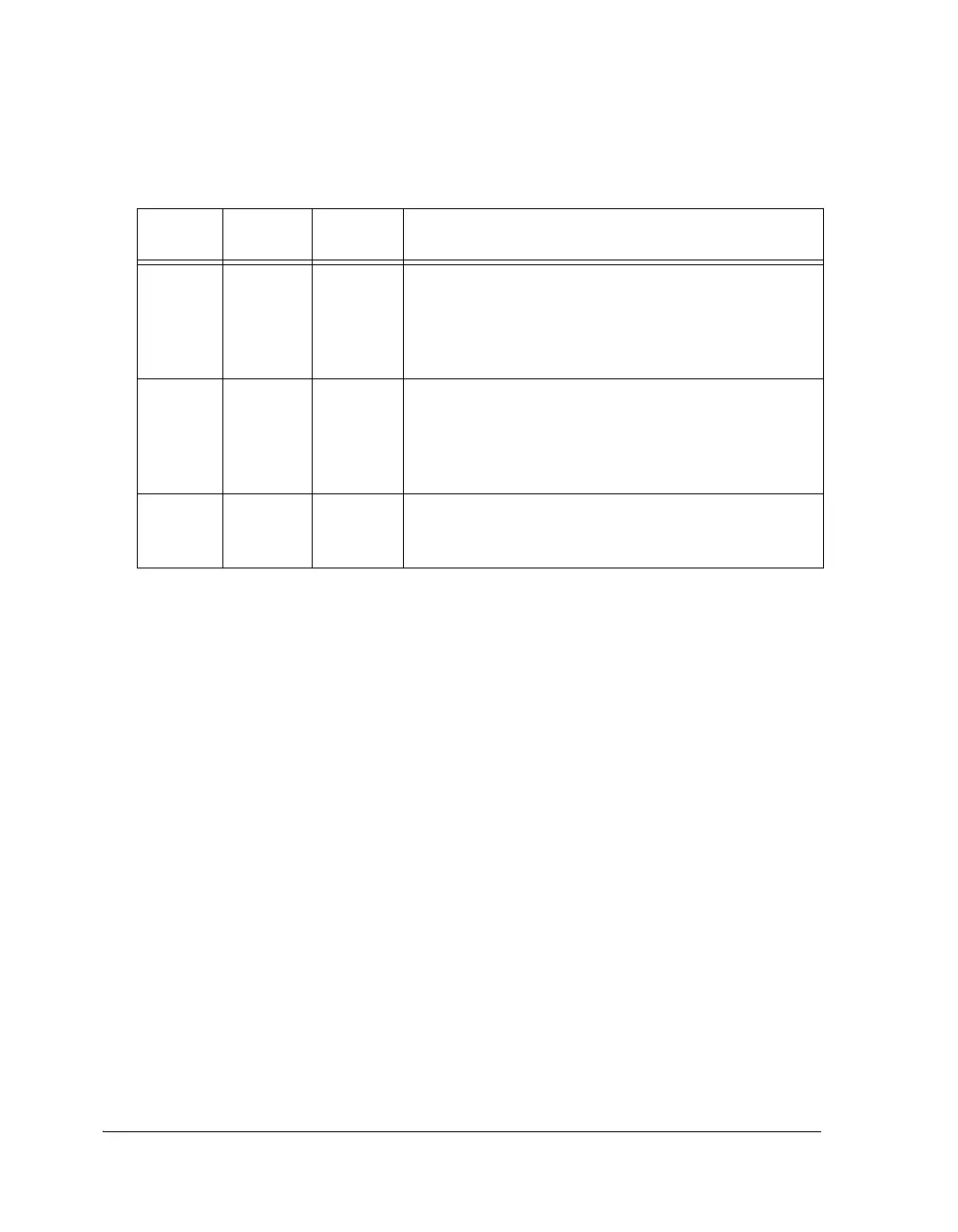

Table 3-4. Data Packing Bit Settings (PKDIS)

Packing

Mode

PKDIS Bit

Setting

MSWF Bit

Setting

Description

Enabled 0 0 8- or 16-bit received data is packed to 32-bit data and

transmitted 32-bit data is unpacked to 2 16-bit data or 4

8-bit data.

First 8- or 16-bit word read/written occupies the least sig-

nificant position in the 32-bit packed word.

Enabled 0 1 8- or 16-bit received data is packed to 32-bit data and

32-bit data to be transmitted is unpacked to 2 16-bit data

or 4 8-bit data. First 8- or 16-bit word read/written occu-

pies the most significant position in the 32-bit packed

word.

Disabled 1 N/A 8- or 16-bit data received is zero filled. For transmitted

data only 16-bit or the 8-bit LSB part of the 32-bit data

word is written to external memory.

Loading...

Loading...