ADSP-214xx SHARC Processor Hardware Reference A-257

Registers Reference

Master Control Register (TWIMCTL)

The TWI master mode control register (

TWIMCTL, shown in Figure A-148

and described in Table A-140) controls the logic associated with master

mode operation. Bits in this register do not affect slave mode operation

and should not be modified to control slave mode functionality.

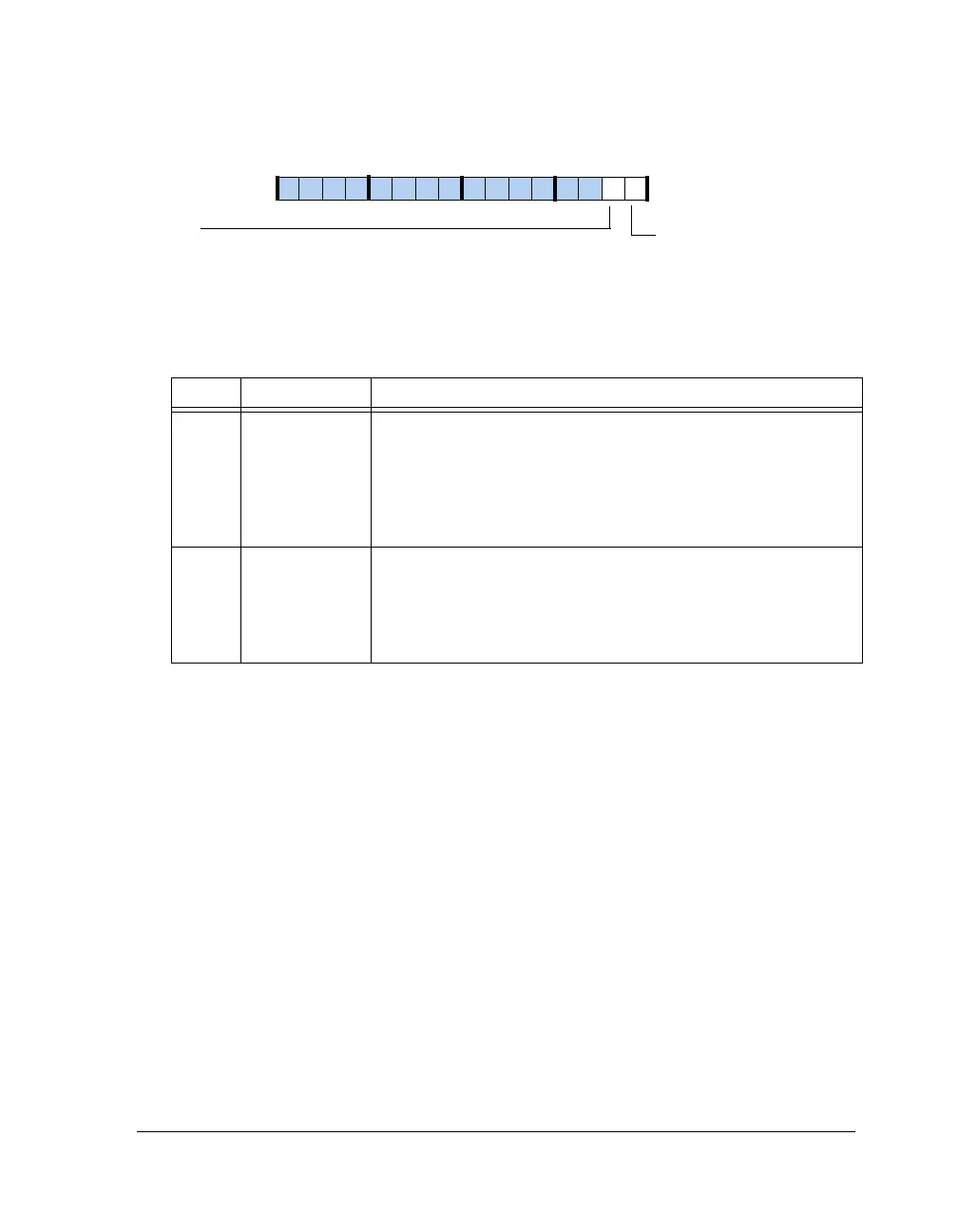

Figure A-147. TWISSTAT Register

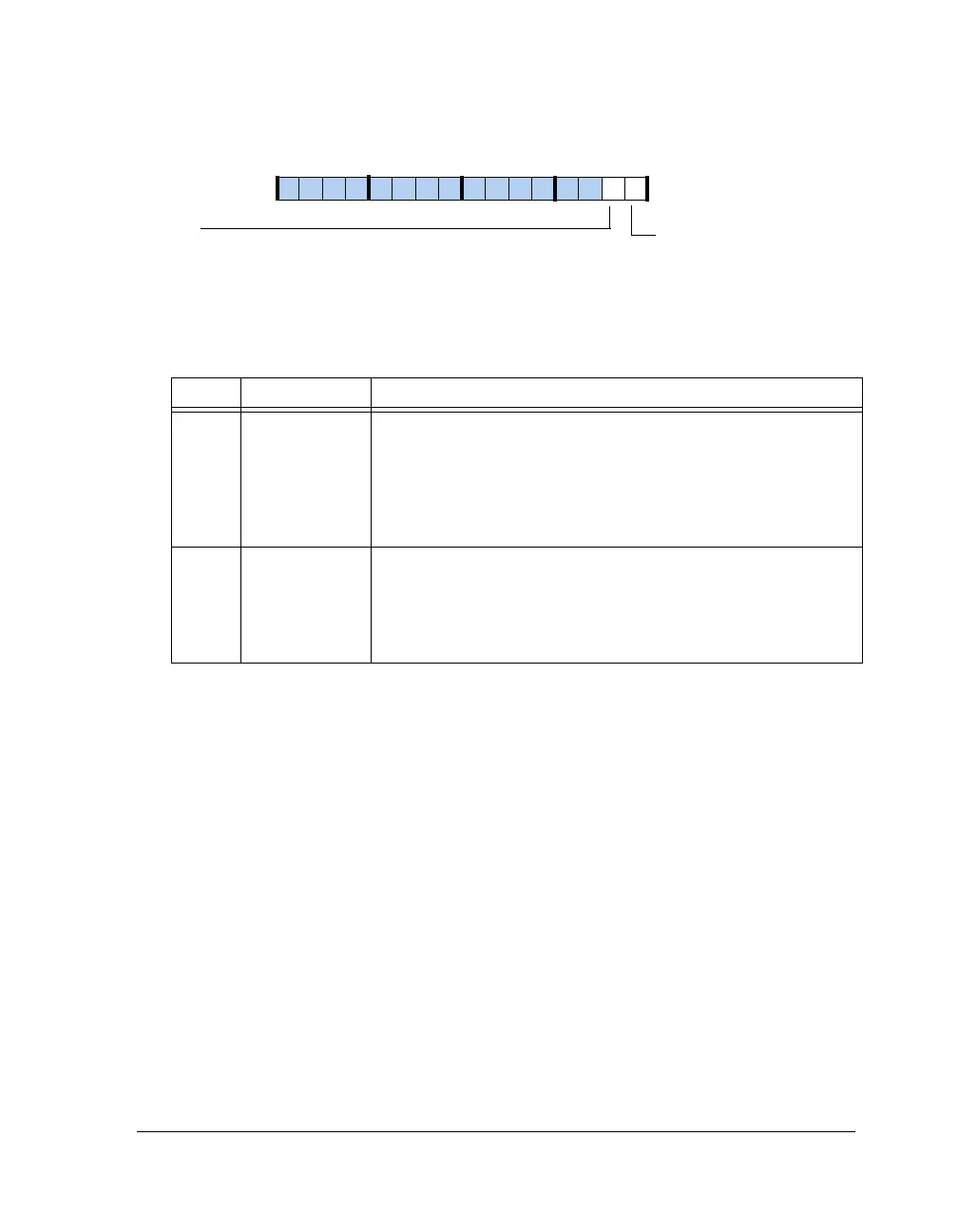

Table A-139. TWISSTAT Register Bit Descriptions (RO)

Bit Name Description

0 TWISIDR Slave Transfer Direction. This bit self clears if slave mode is disabled

(SEN = 0)

0 = At the time of addressing, the transfer direction was determined

to be slave receive.

1 = At the time of addressing, the transfer direction was determined

to be slave transmit.

1TWIGC General Call. This bit self clears if slave mode is disabled (SEN = 0)

0 = At the time of addressing, the address was not determined to be a

general call.

1 = At the time of addressing, the address was determined to be a gen-

eral call.

TWISDIR

Slave Transfer Direction

09 837564 2114 12 11 101315

TWIGC

General Call

Loading...

Loading...