Operating Modes

16-8 ADSP-214xx SHARC Processor Hardware Reference

Pulse Width Modulation Mode (PWM_OUT)

In PWM_OUT mode, the timer supports on-the-fly updates of period and

width values of the PWM waveform. The period and width values can be

updated once every PWM waveform cycle, either within or across PWM

cycle boundaries.

To enable PWM_OUT mode, set the TIMODE1–0 bits to 01 in the timer’s con-

figuration (TMxCTL) register. This configures the timer’s TIMERx signal as

an output with its polarity determined by PULSE as follows:

•If PULSE is set (= 1), an active high width pulse waveform is gener-

ated at the TIMERx signal.

•If

PULSE is cleared (= 0), an active low width pulse waveform is gen-

erated at the

TIMERx signal.

The timer is actively driven as long as the TIMODE field remains 01.

Figure 16-2 shows a flow diagram for

PWM_OUT mode. When the timer

becomes enabled, the timer checks the period and width values for plausi-

bility (independent of the value set with the

PRDCNT bit) and does not start

to count when any of the following conditions are true:

• Width is equal to zero

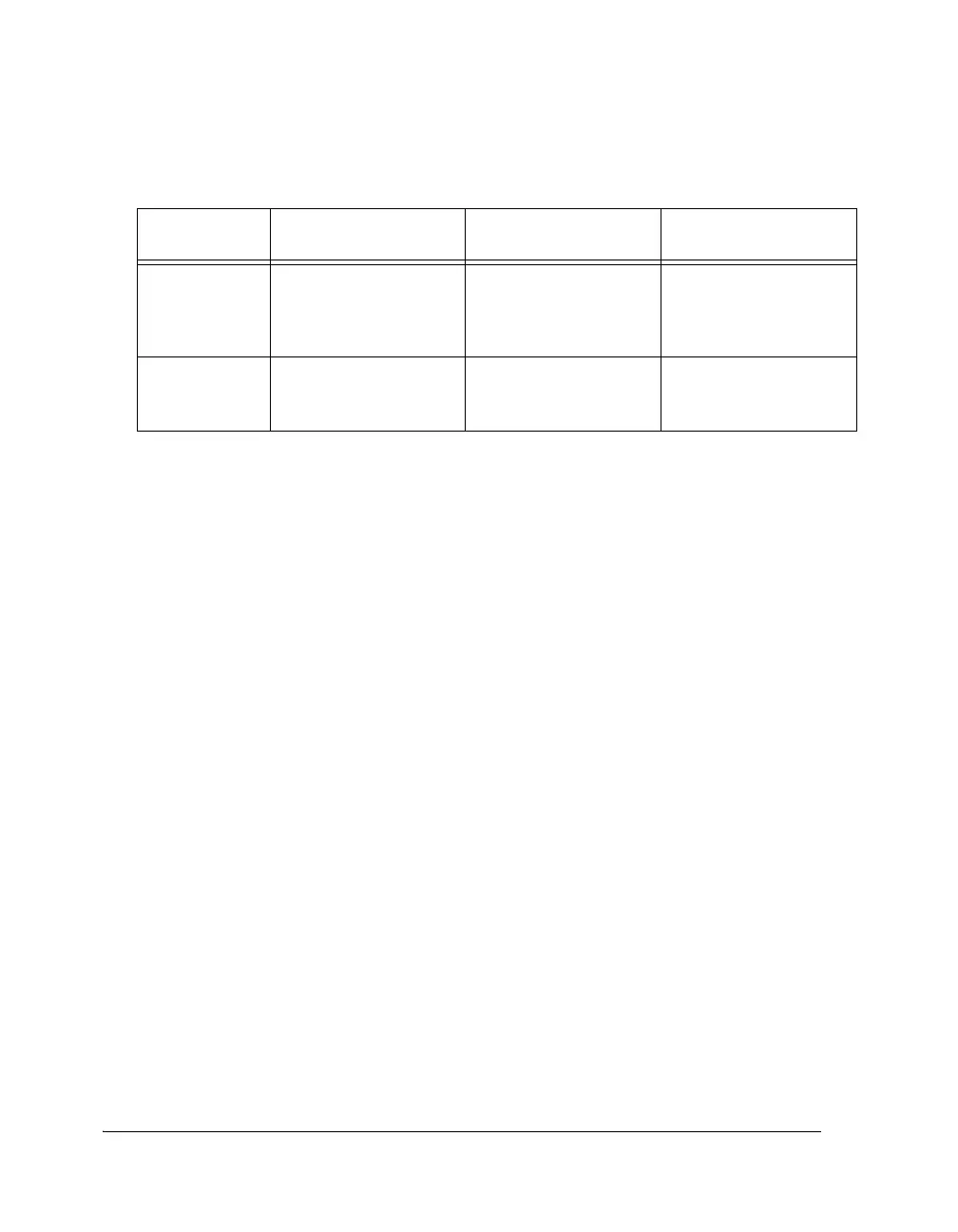

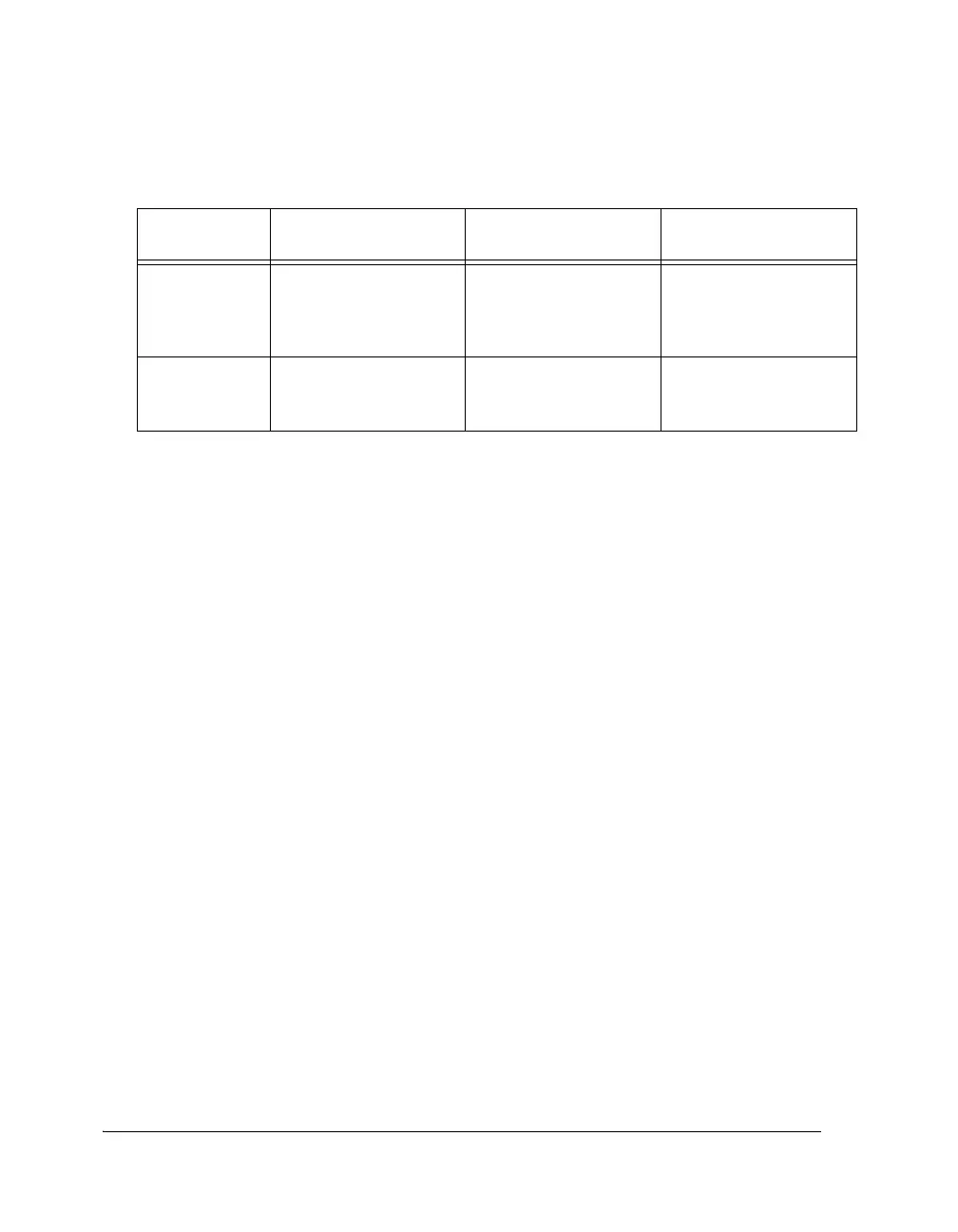

TMxOVF

(IRQ also set)

Set if Initialized with:

Period < Width or

Period == Width or

Period == 0

Set if the Counter wraps

(Error Condition)

Unused

TMxIRQ

(If enabled)

If PERIOD_CNT:

1 = Set at end of Period

0 = Set at end of Width

If PERIOD_CNT:

1 = Set at end of Period

0 = Set at end of Width

Set after Period Expires

and PCLK is running

Table 16-4. Timer Signal Use (Cont’d)

Register

Settings

PWM_OUT Mode WIDTH_CAP Mode EXT_CLK Mode

Loading...

Loading...