ADSP-214xx SHARC Processor Hardware Reference 3-73

External Port

Multibank access reduces precharge and activation cycles by map-

ping opcode/data among different internal DDR2 banks driven by

the (DDR2_BA2-0) pins and external memory selects (DDR2_CS3-0).

Multi Bank Operation with Data Packing

A logical address correspond to 2 physical addresses. Consequently a phys-

ical address for example of 1024 x 16 page size translates into a logical

address of 512 x 16 words to satisfy the packing. According to this all row

addresses are shifted by 2.

A populated DDR2 of 8M x 16 x 8 with 1K words page size connected to

external bank 0 has a logical mapping as follows.

Page Interleaving (DDR2ADDRMODE bit = 0):

0x200000 logical start address int bankA

0x2001FF logical end address int bankA

0x200200 logical start address int bankB

0x2003FF logical end address int bankB

0x200400 logical start address int bankC

0x2005FF logical end address int bankC

0x200600 logical start address int bankD

0x2007FF logical end address int bankD

0x200800 logical start address int bankE

0x2009FF logical end address int bankE

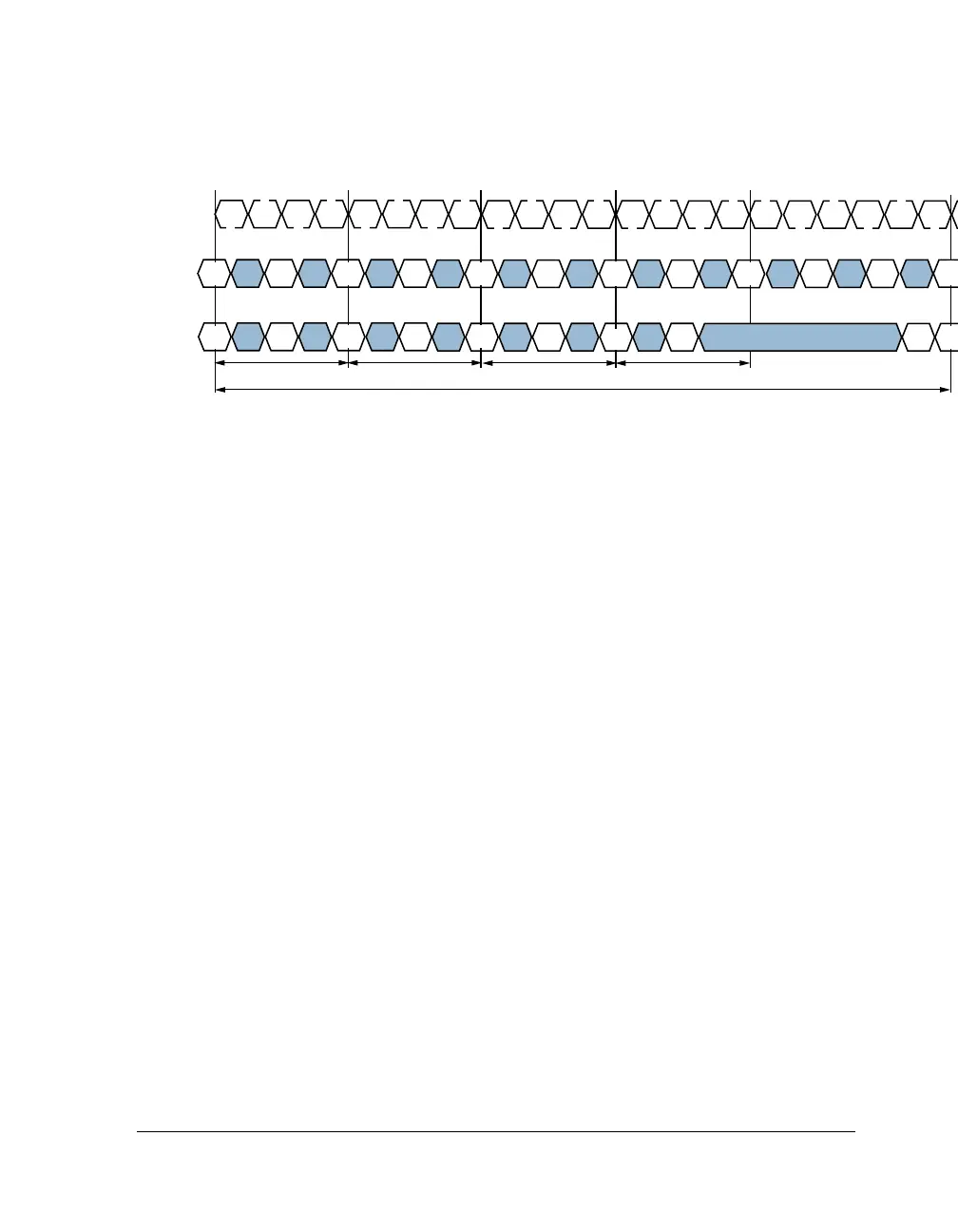

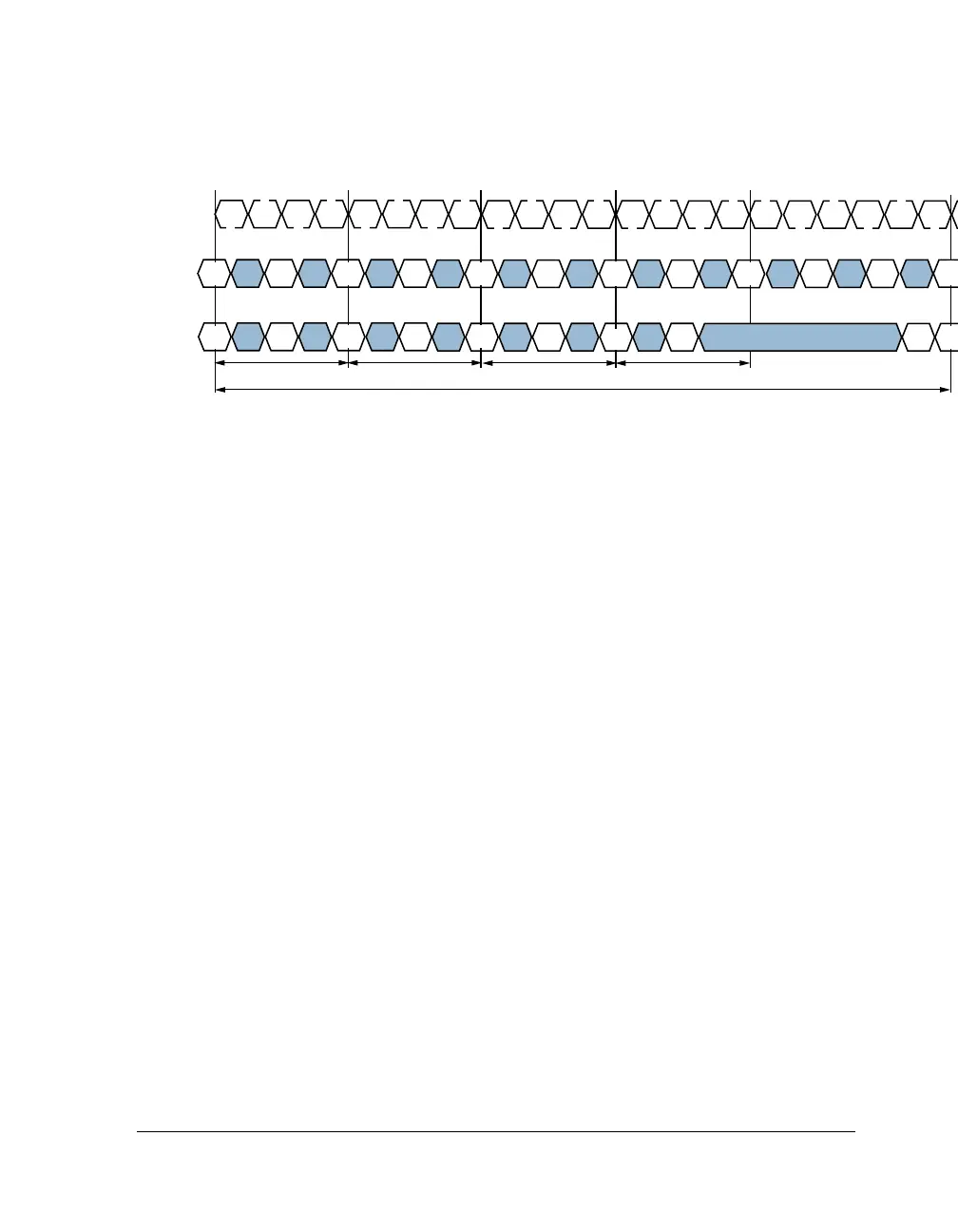

Figure 3-17. Bank Activation for a 8 Banked Device

T0 T1 T4 T5T2 T3 T7 T8T6

T9

t

RDD(min)

DDR2_CLKx

DDR2_CLKx/

T10

T11

Bank

a

Bank

b

Bank

c

Bank

c

Bank

d

Bank

e

ACT

Bank

a

Bank

b

ACT ACTACT

ACT

COMMAND

BA0, BA1,

BA2

t

RDD(min)

t

RDD(min)

t

RDD(min)

READ READ READ READ

NOP NOP NOP

Loading...

Loading...