Features

4-2 ADSP-214xx SHARC Processor Hardware Reference

Features

These bidirectional ports have eight data lines, an acknowledge line, and a

clock line. The maximum frequency of operation of the link ports is 166

MHz. The link port clock to core clock ratio programming is applicable

only if the link port is configured as transmitter. The receiver link port

can operate at any asynchronous clock frequency up to 166 MHz (or

peripheral clock frequency (PCLK = CCLK/2) which ever is lower) indepen-

dent of the programmed ratio.

The link ports contain the features shown in the following list.

• Operate independently and simultaneously.

• Pack data into 32-bit words; this data can be directly read by the

processor or DMA-transferred to or from on-chip memory.

• Have double-buffered transmit and receive data registers.

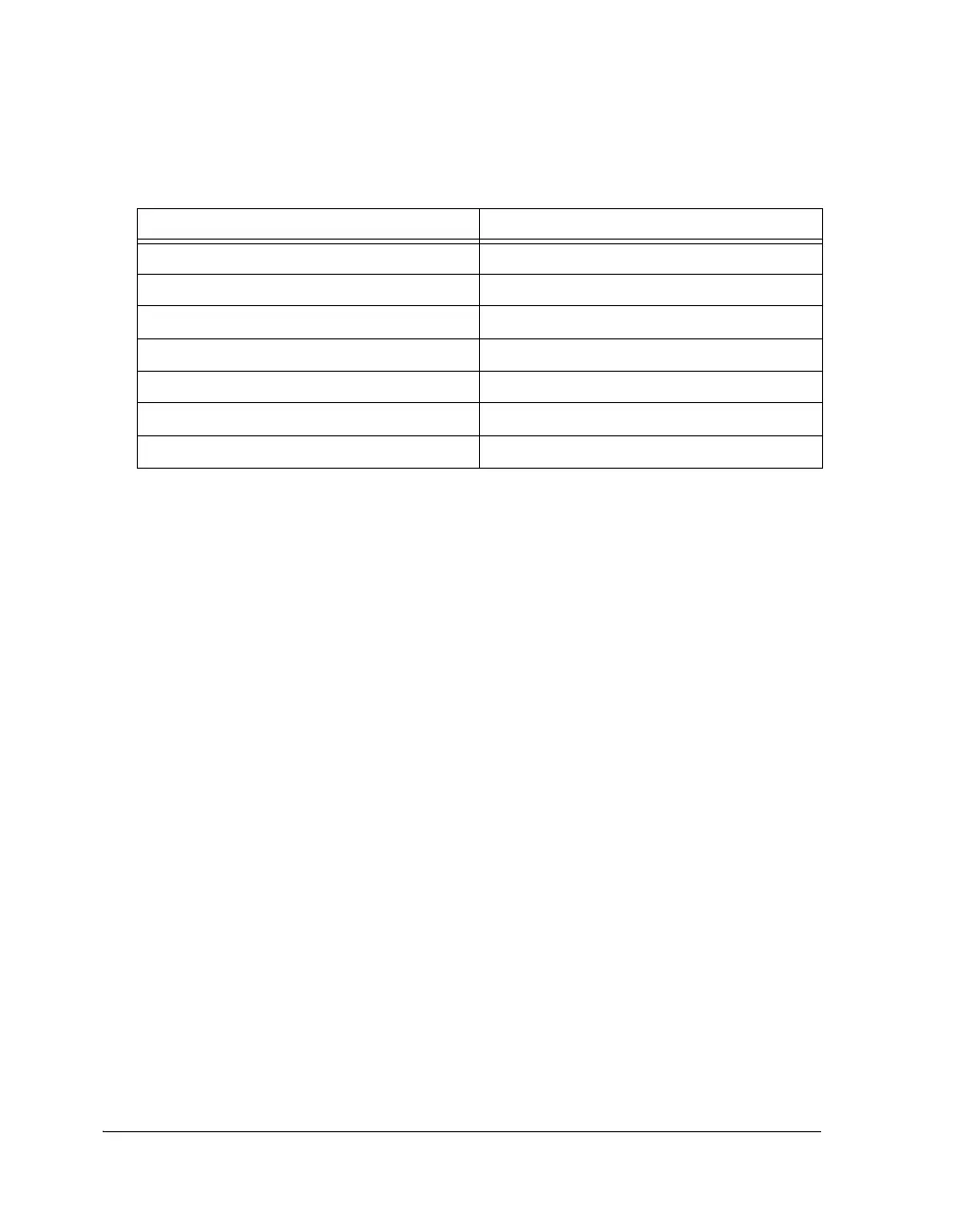

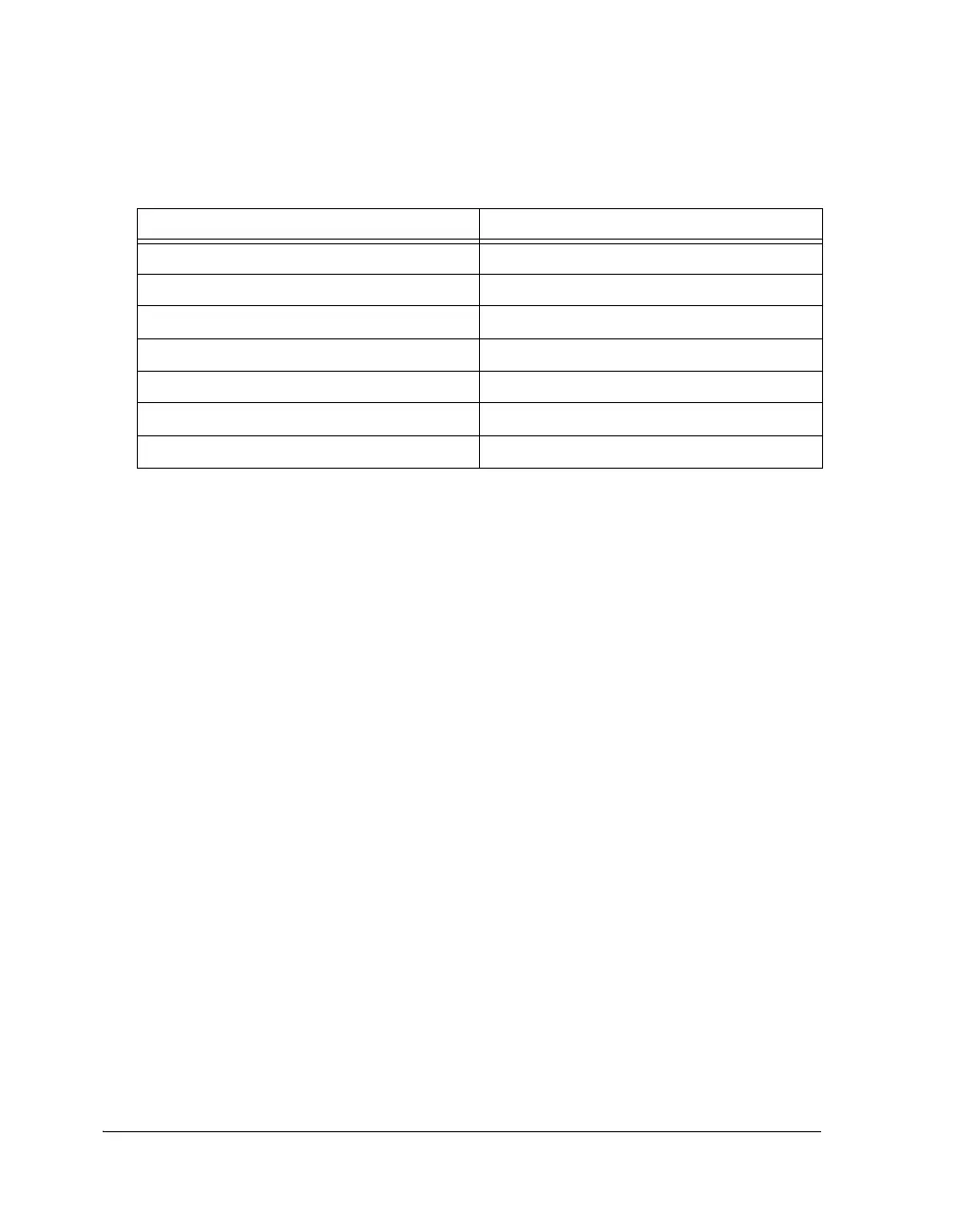

Core Data Access Yes

DMA Data Access Yes

DMA Channels 2

DMA Chaining Yes

Boot Capable Yes (Link Port 0)

Local Memory No

Clock Operation LCLK

Table 4-1. Link Port Specifications (Cont’d)

Feature Link Port1–0

Loading...

Loading...