ADSP-214xx SHARC Processor Hardware Reference 2-11

I/O Processor

Some data buffers provide debug support to enable the buffer hang disable

(

BHD) bit. This feature can be enabled in the dedicated peripheral control

register for the IDP, SPORT, link port, UART0 and the TWI.

Chain Pointer Registers

The chain pointer registers, described in Table 2-10 (generic), Table 2-11

(SPORTs) and Table 2-12 (external port) are 20 bits wide. The lower 19

bits are the memory address field. Like other I/O processor address regis-

ters, the chain pointer register’s value is offset to match the starting

address of the processor’s internal memory before it is used by the I/O

processor. On the SHARC processor, this offset value is 0x80000.

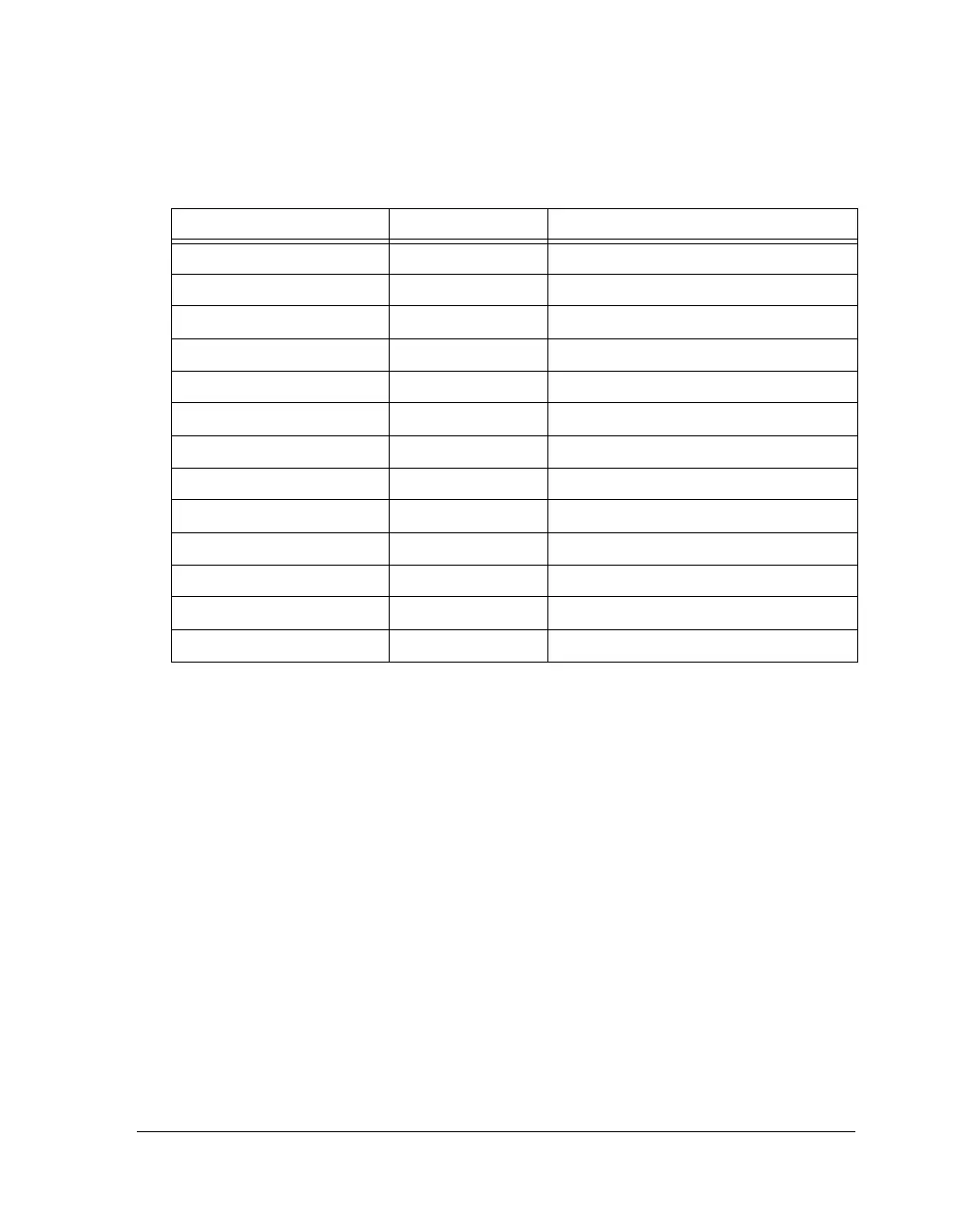

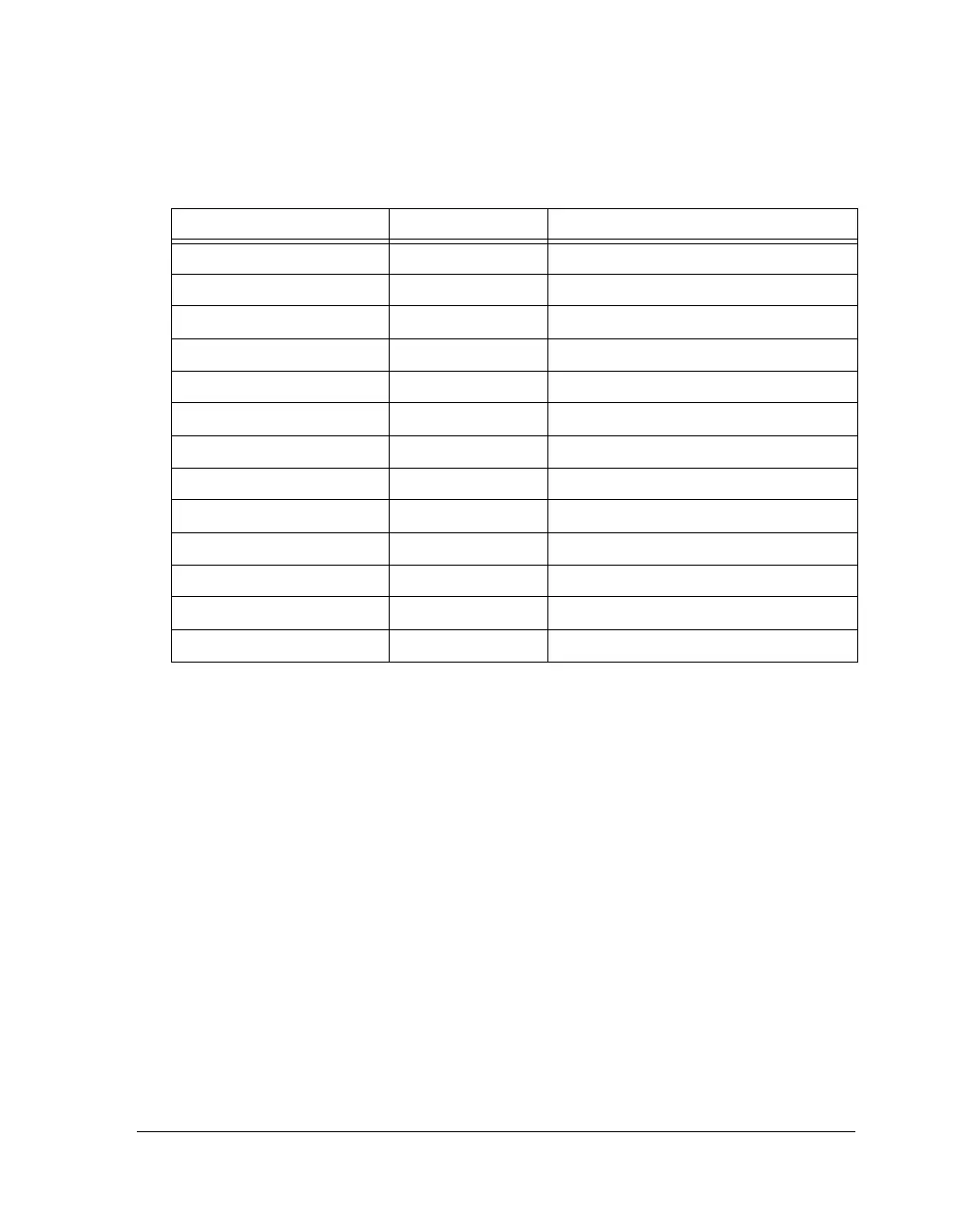

UARTRBR0 1 UART0 Receiver

UARTTHR0 1 UART0 Transmitter

Accelerator input 8 FFT DMA only

Accelerator output 8 FFT DMA only

MTM read/write 2 DMA only

DFEP0–1 6 DMA only

AMIRX 1 AMI Receive Packer

AMITX 1 AMI Transmit Packer

TXTWI8 1 (1 byte) TWI Transmit

TXTWI16 1 (2 bytes) TWI Transmit

RXTWI8 1 (1 byte) TWI Receive

RXTWI16 1 (2 bytes) TWI Receivet

MLB local buffer 124 MLB SRAM

Table 2-9. Data Buffers (Cont’d)

Buffer Name FIFO Depth Description

Loading...

Loading...