ADSP-214xx SHARC Processor Hardware Reference 23-21

System Design

to 384 words. Since one 32-bit word is created from four packed 8-bit

words, the total number of 8-bit words transmitted is 1536.

Link Port Booting

Booting is supported through link port 0. The BOOT_CFG2–0 values for

selecting link port boot is 100.

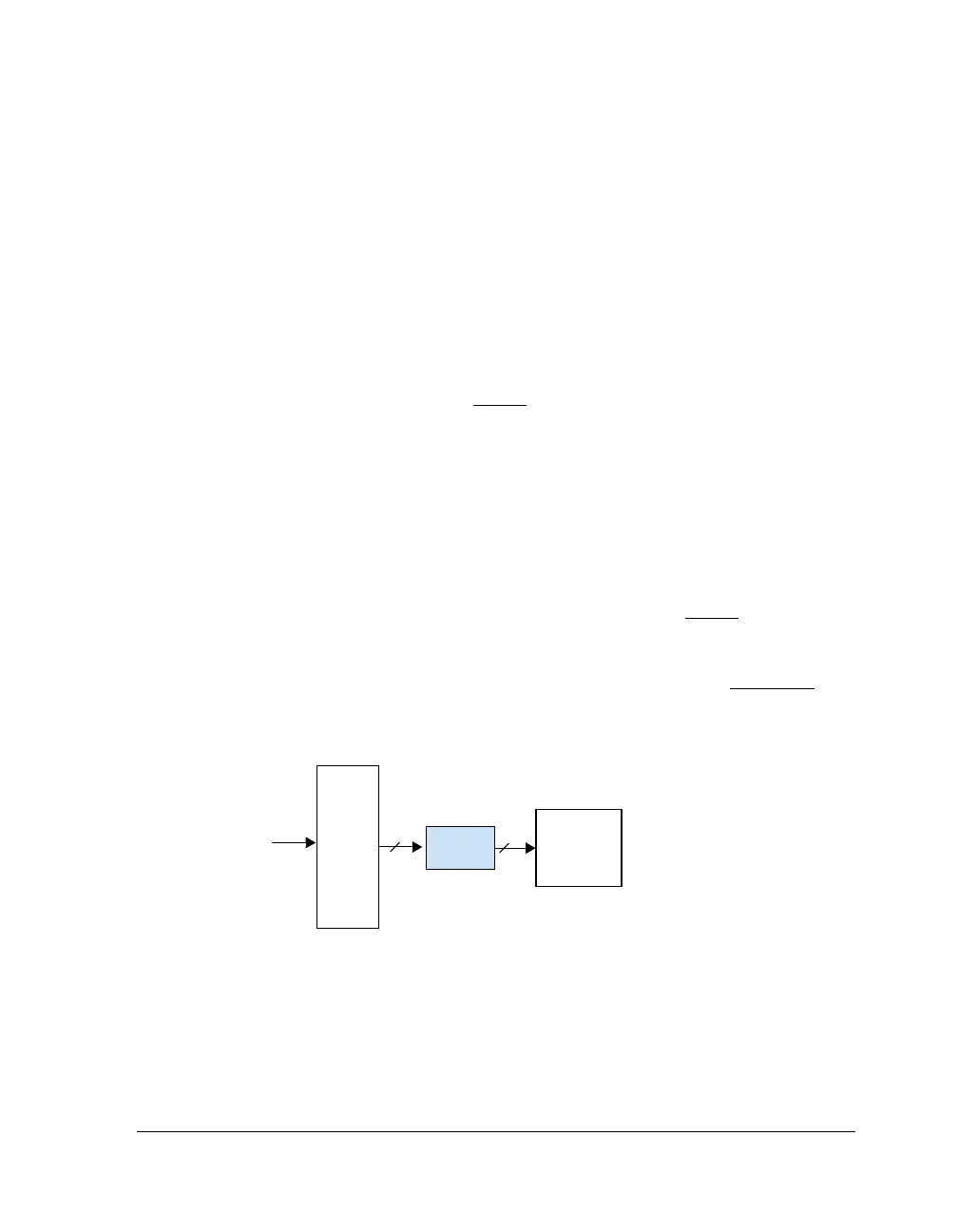

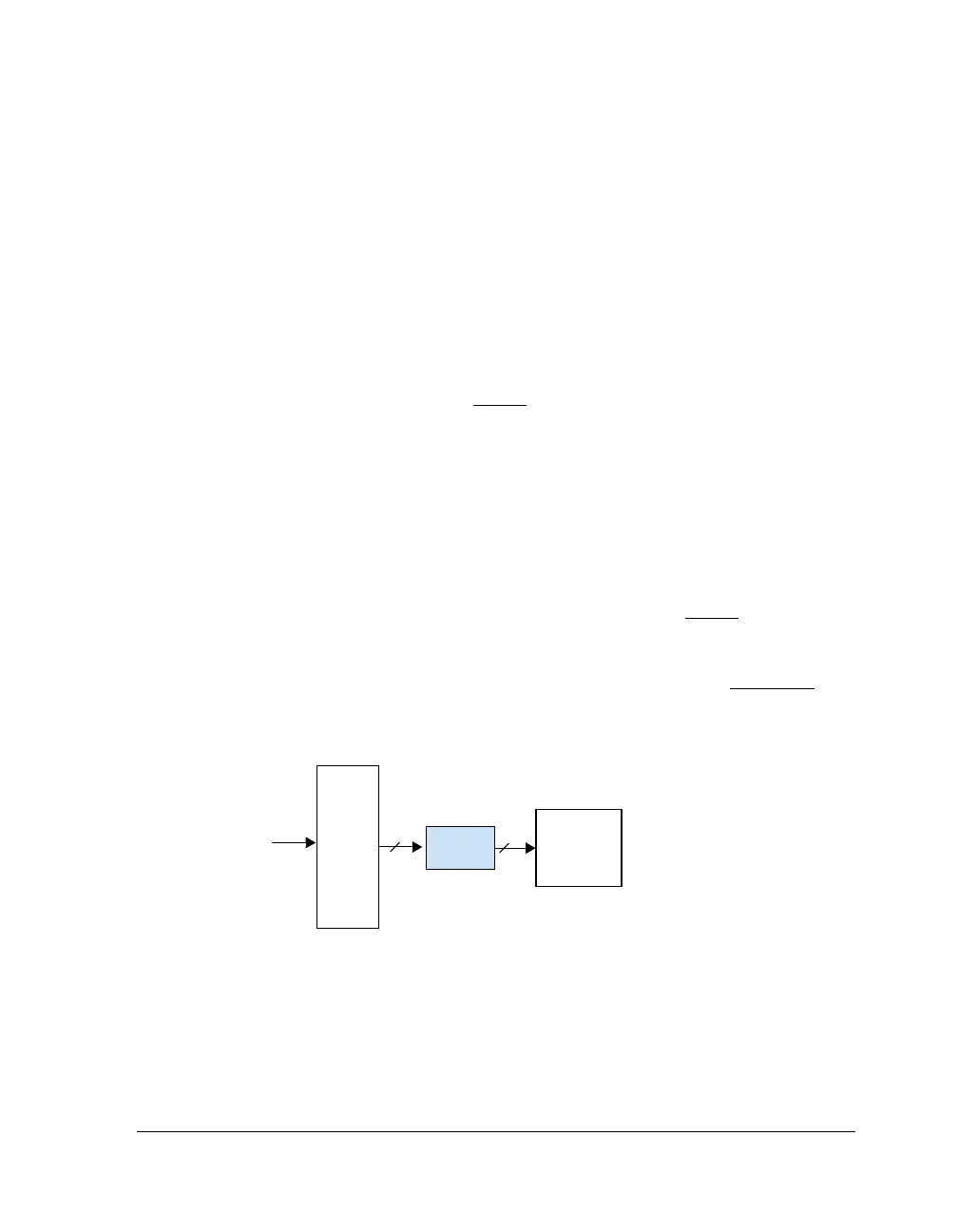

The booting procedure is the same as any other boot mode. The acknowl-

edge signal (LACK0) is asserted at RESET since the link port is configured as

a receiver. The host initiates the transfer by toggling the link port clock

(LCLK0). Boot data is shifted in 8-bits every clock cycle through the LDAT0x

pins. The received data streams of 4 x 8-bit is packed by the 2 deep RXLP0

buffer into 32-bit words, least significant bit (LSB) first, and passed into

the internal memory (Figure 23-9). Once the DMA is completed, a link

port 0 interrupt (P1I) occurs. If BOOT_CFG2–0 is 100 (link port 0 boot),

P1I is programmed as link port 0 interrupt at reset and the interrupt is

unmasked at reset. Otherwise, P1I is programmed as an SPIHI interrupt at

reset.

For link port boot, LCK0 should only be asserted after RESETOUT has

deasserted.

Figure 23-9. Link Port Data Packing

RXLP0

Internal

Memory

32

32

DMA

8-bit to 32-bit packing

LDATA[7:0]

Loading...

Loading...