ADSP-214xx SHARC Processor Hardware Reference A-203

Registers Reference

Transmit User Bits Buffer Registers for Subframe A/B

Registers (DITUSRBITAx/Bx)

Once programmed, these registers are used only for the next block of data.

This allows programs to change the user bit information with every block

of data. After writing to the appropriate registers to change the user bits

for the next block, DITUSRBITAx and DITUSRBITBx must be written to

enable the use of these bits. Note these registers are used in standalone

mode only.

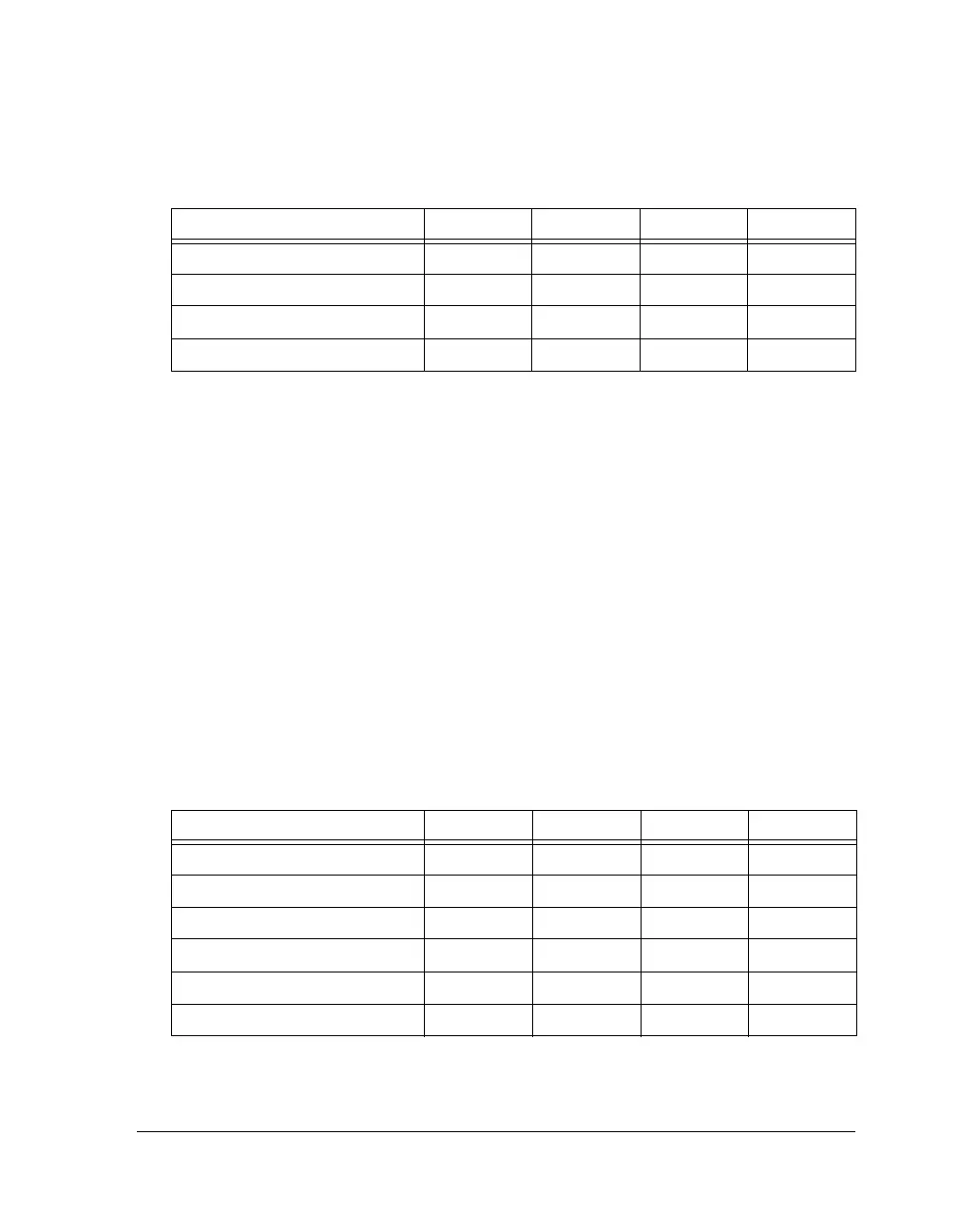

There are six user bits buffer registers associated with subframe A (left

channel) and six user bits buffer registers associated with subframe B

(right channel). These registers are listed with their locations in

Table A-107 and Table A-108.

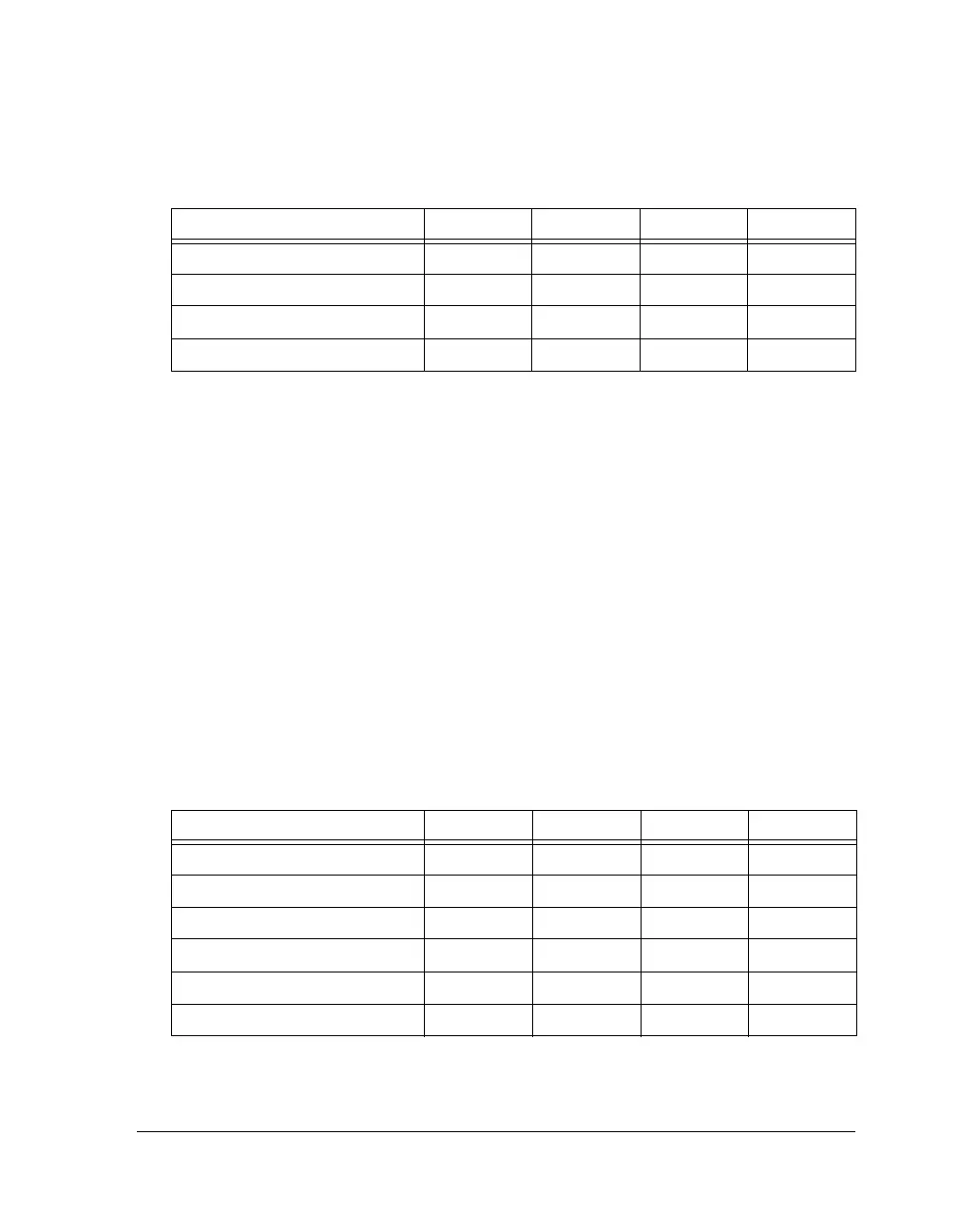

DITCHANB2 BYTE9 BYTE10 BYTE11 BYTE12

DITCHANB3 BYTE13 BYTE14 BYTE15 BYTE16

DITCHANB4 BYTE17 BYTE18 BYTE19 BYTE20

DITCHANB5 BYTE21 BYTE22 BYTE23 Reserved

Table A-107. DITUSRBITAx Registers (RW)

Register Bits 7–0 Bits 15–8 Bits 23–16 Bits 31–24

DITUSRBITA0 BYTE0 BYTE1 BYTE2 BYTE3

DITUSRBITA1 BYTE4 BYTE5 BYTE6 BYTE7

DITUSRBITA2 BYTE8 BYTE9 BYTE10 BYTE11

DITUSRBITA3 BYTE12 BYTE13 BYTE14 BYTE15

DITUSRBITA4 BYTE16 BYTE17 BYTE18 BYTE19

DITUSRBITA5 BYTE20 BYTE21 BYTE22 BYTE23

Table A-106. DITCHANBx Registers (RW) (Cont’d)

Register Bits 7–0 Bits 15–8 Bits 23–16 Bits 31–24

Loading...

Loading...