ADSP-214xx SHARC Processor Hardware Reference 20-15

UART Port Controller

Interrupt Routing

The following sections describe the various possibilities for routing a

UART interrupt to the interrupt vector table (IVT).

DPI

The UART interrupts are all combined into the digital peripheral inter-

face (DPI) interrupt. The DPI_IRPTL register determines whether an

interrupt is for the transmitter or receiver. Listing 20-1 shows an example

of how to enable the UART over the DPI.

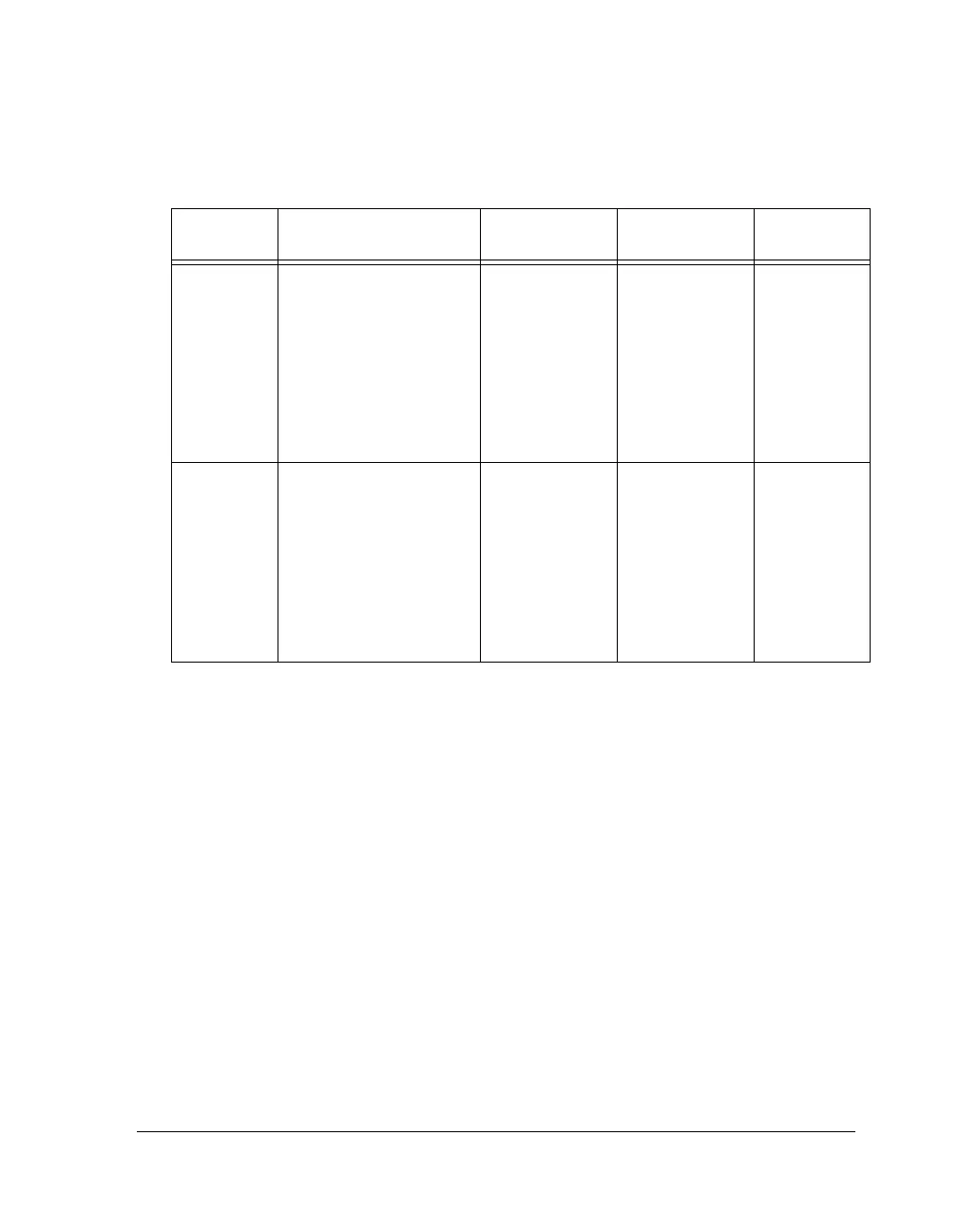

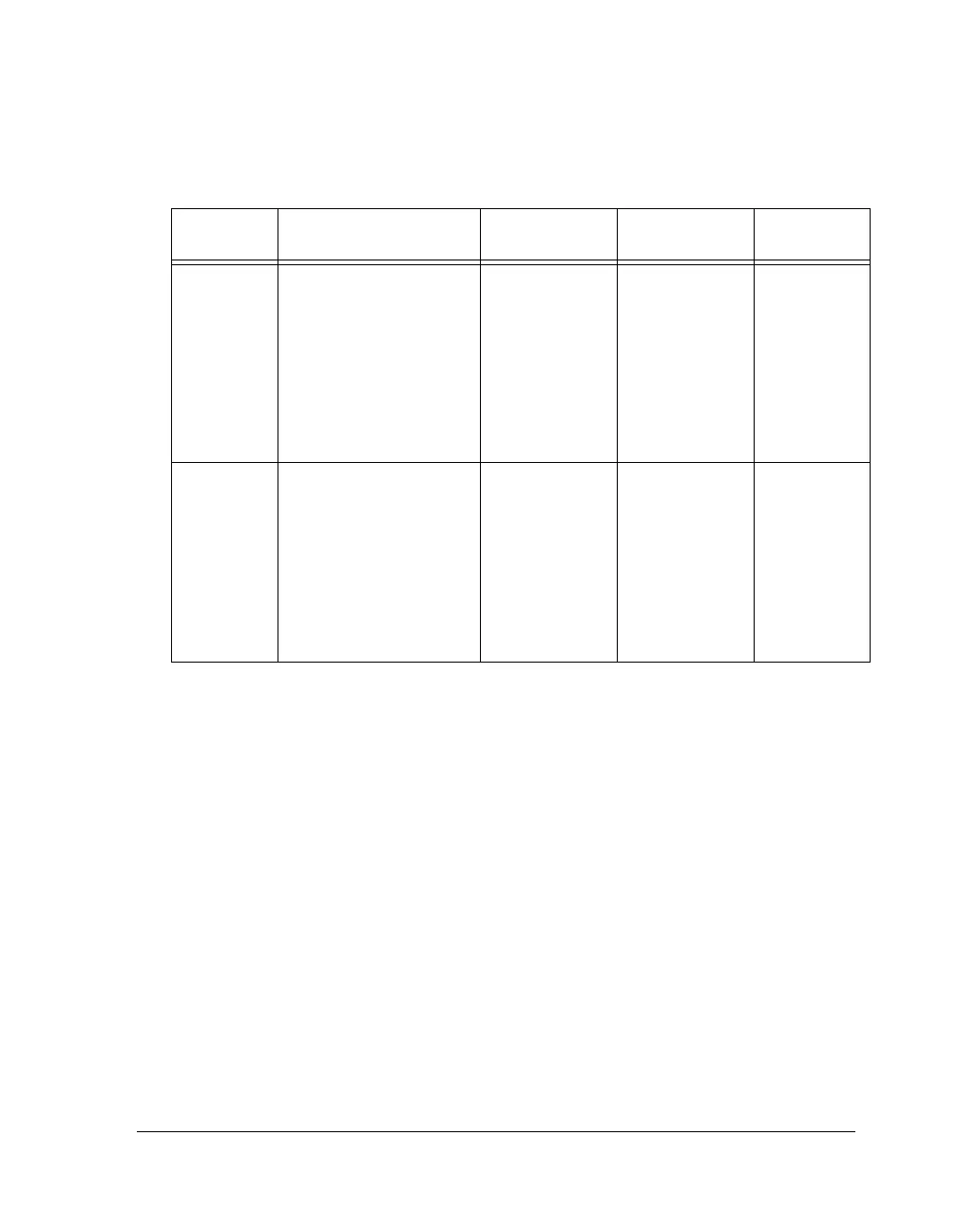

Table 20-4. UART Interrupt Overview

Interrupt

Source

Interrupt Condition Interrupt

Completion

Interrupt

Acknowledge

Default IVT

DPI UART

(TX/RX)

– DMA RX/TX done

– Core RX buffer full

– Core TX buffer empty

– Core RX Error (overrun,

parity, framing, break)

– DMA RX Error (overrun,

parity, framing)

– Core/DMA 9-bit

addressing

Internal transfer

completion

For UART DMA:

Read to clear

DPI_IMASK

+ RTI instruction

For UART core

(RX INT): Read

to clear

UARTxIIR + RTI

instruction

P14I

UART

(TX/RX)

– DMA RX/TX done

– Core RX buffer full

– Core TX buffer empty

– Core RX Error (overrun,

parity, framing, break)

– DMA RX Error (overrun,

parity, framing)

– Core/DMA 9-bit

addressing

Internal transfer

completion

For UART DMA:

RTI instruction

For UART core

(RX INT): Read

to clear

UARTxIIR + RTI

instruction

Need to route

UARTTXI

UARTRXI

(PICRx) to

any PxxI

Loading...

Loading...