Features

12-2 ADSP-214xx SHARC Processor Hardware Reference

Features

The SRC for the SHARC processors has the features shown in the list

below.

• 4 sample rate converters

• Automatically senses sample frequencies

• Simple programming required

• Attenuates sample clock jitter

• Supports left-justified, I

2

S, right-justified (16-,18-, 20-, 24-bits),

and TDM serial port (daisy chain) modes

• Accepts 16-/18-/20-/24-bit data

• Up to 192 kHz sample rate input/output sample ratios from 7.75:1

to 1:8

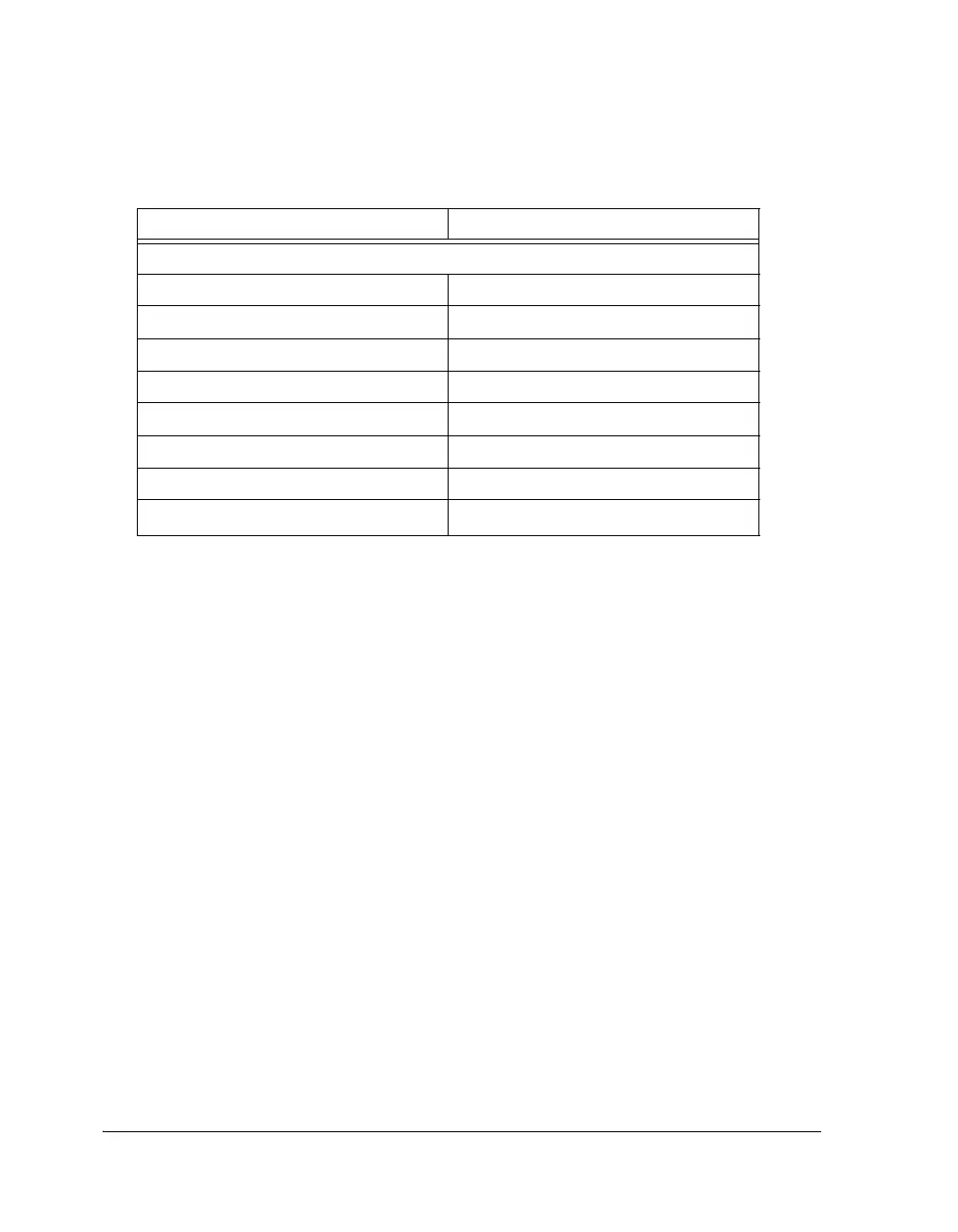

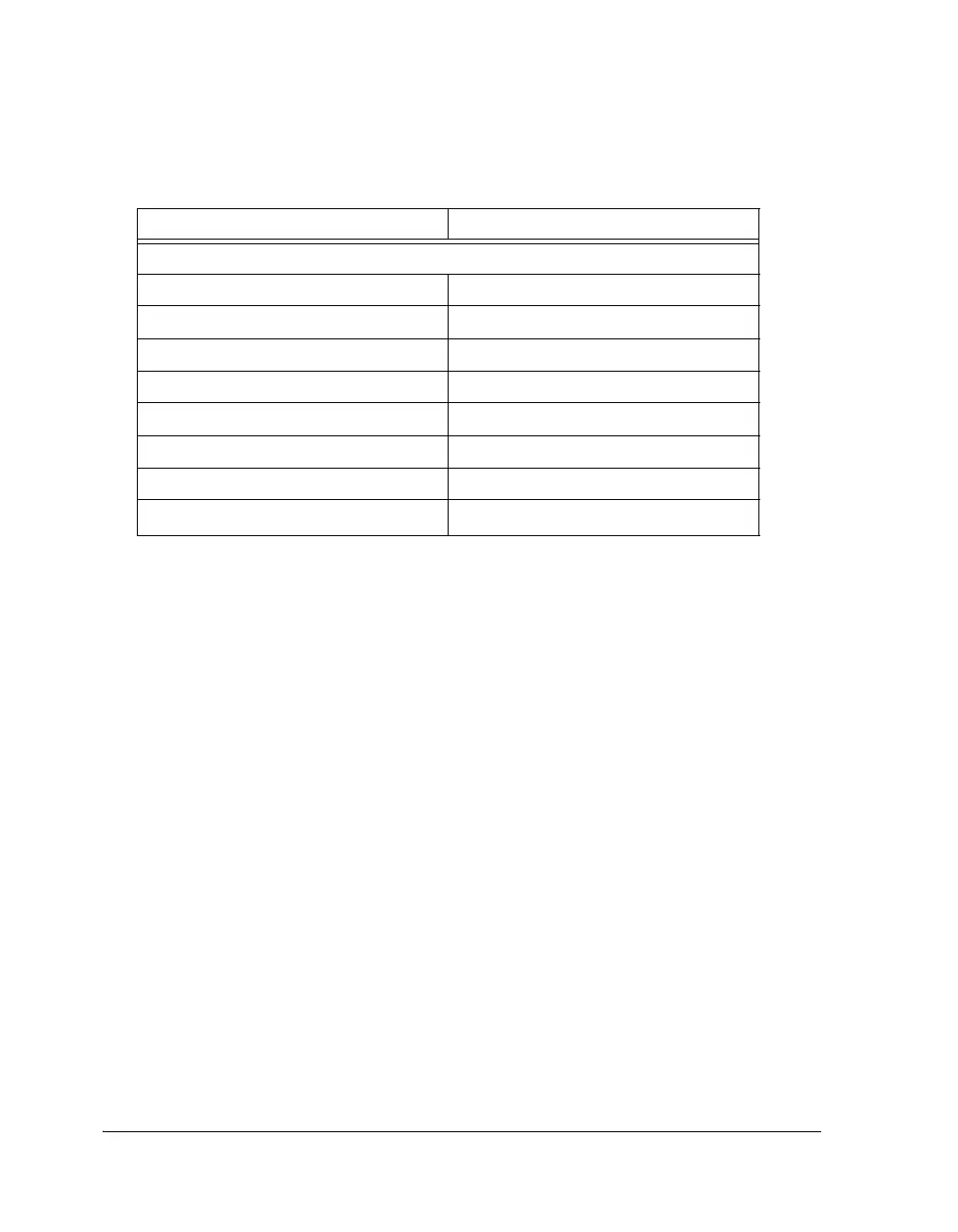

Access Type

Data Buffer No

Core Data Access N/A

DMA Data Access N/A

DMA Channels N/A

DMA Chaining N/A

Boot Capable N/A

Local Memory Yes (RAM, ROM)

Clock Operation f

PCLK

/4

Table 12-1. SRC Specifications (Cont’d)

Feature Availability

Loading...

Loading...