Peripherals Routed Through the DAI

A-172 ADSP-214xx SHARC Processor Hardware Reference

port is configured as transmitter. If the serial port is configured as the

receiver it ignores the incoming data.

SPORT Compand Registers (MTxCCSy or MRxCCSy)

Each bit, 31–0, set (=1) in one of the four

MTxCCS0, MTxCCS1, MTxCCS2,

MTxCCS3 for SPORT/0/2/4/6 and MRxCCS0, MRxCCS1, MRxCCS2, MRxCCS3 for

SPORT1/3/5/7 registers corresponds to a companded channel, 127–0, on

a multichannel mode serial port. When these registers activate compand-

ing for a channel, the SPORT applies the companding from the serial

port’s DTYPE selection to the word transmitted or received in that channel’s

position of the data stream. When a channel’s bit in these registers is

cleared (=0), the SPORT does not compand the outgoing or incoming

data during the channel’s time slot.

Error Control Register (SPERRCTLx)

The SPERRCTLx registers control and report the status of the interrupts

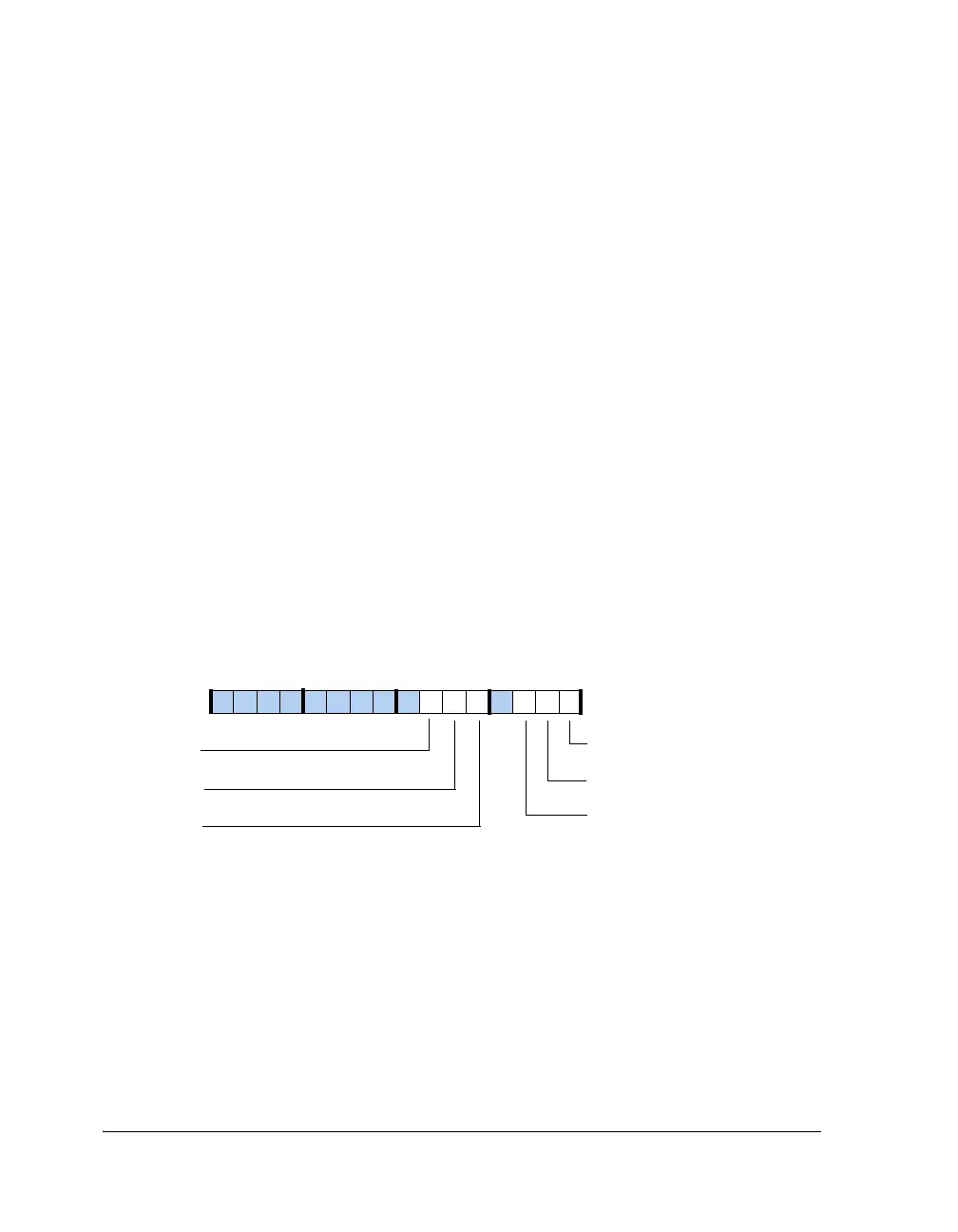

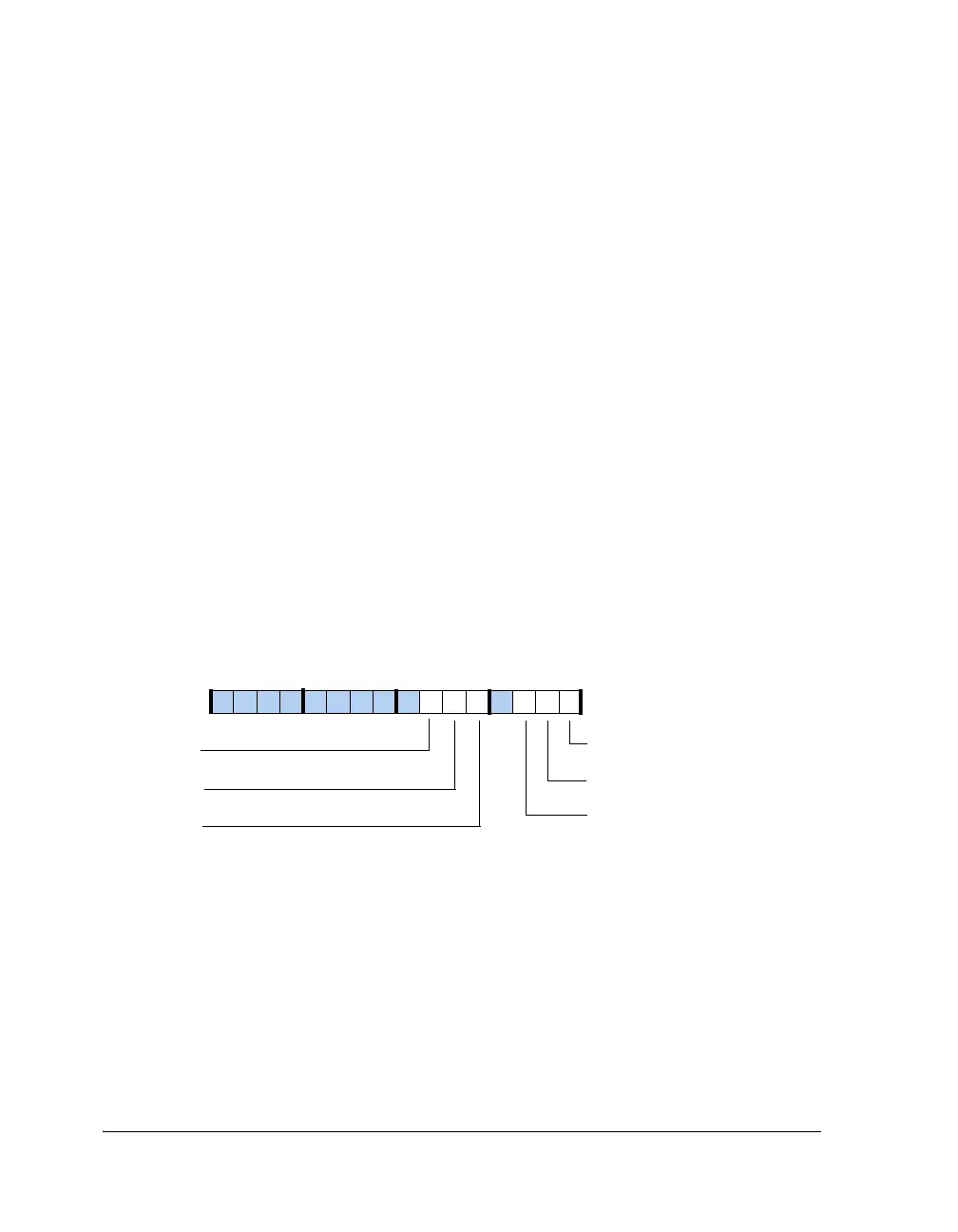

generated by each SPORT (see Figure A-91, Table A-89).

Figure A-91. SPERRCTLx Register

DERRA_EN

DERRB_EN

FSERR_EN

DERRB_STAT

DERRA_STAT

FSERR_STAT

Enable Channel A Error Detection

Enable Channel B Error Detection

Enable Frame Sync Error Detection

Channel B Interrupt Status

Channel A Interrupt Status

Frame Sync Interrupt Status

09 837564 2114 12 11 101315

Loading...

Loading...