Interrupts

2-48 ADSP-214xx SHARC Processor Hardware Reference

interrupt-driven I/O under control of the processor core. Refer to the spe-

cific peripheral chapter for more information.

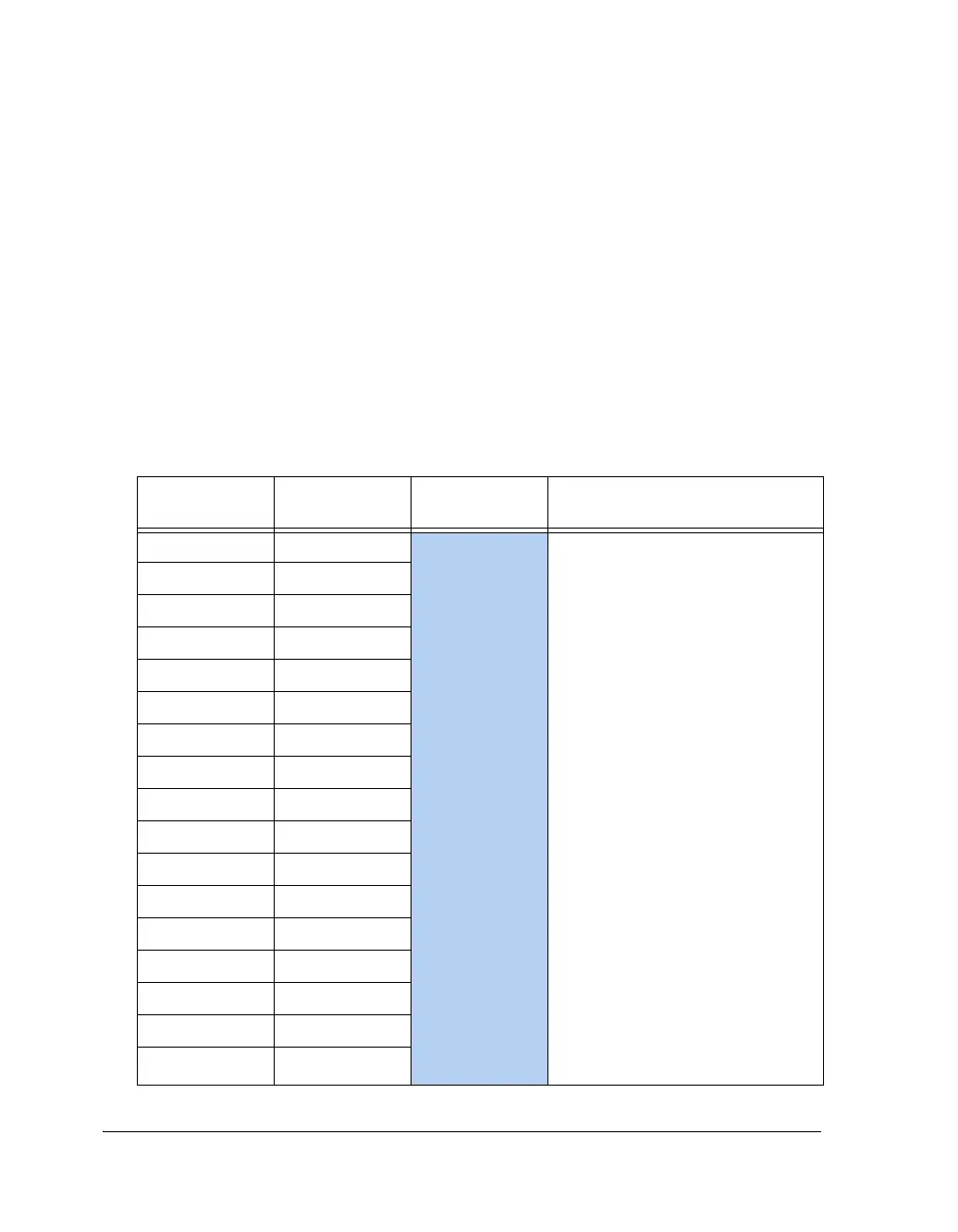

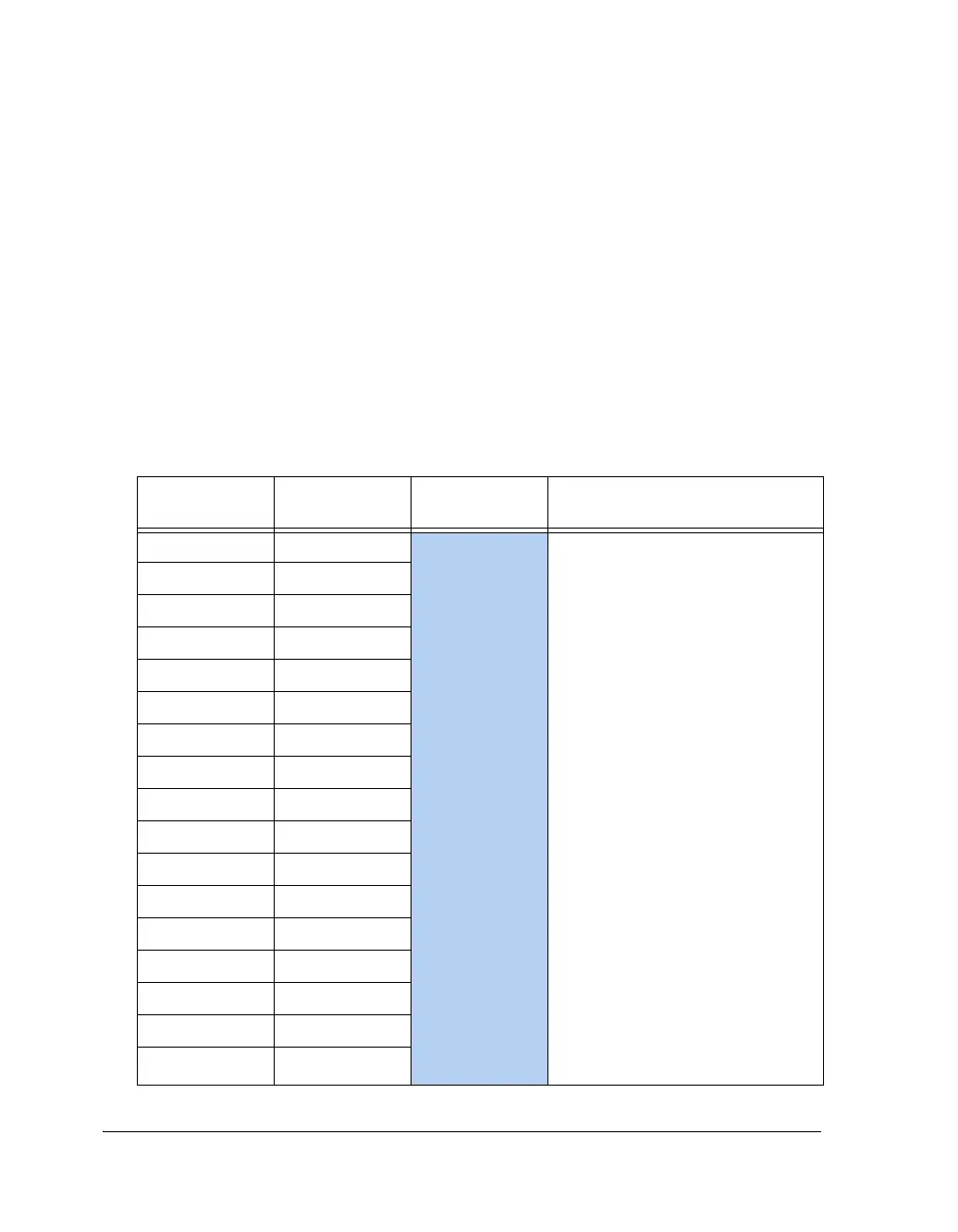

Interrupt Versus Channel Priorities

At their default setting shown in Table 2-29, the DMA interrupt priorities

do not match the DMA channel priorities. However, if both priorities

schemes should match, the DMA interrupt priorities can be re-assigned by

dedicated settings of the PICRx registers.

Table 2-29. Default Channel vs. Interrupt Priorities

Programmable

Interrupt

Default Interrupt

Priority

Priorities DMA Channel Priority

P0I DAIHI

Highest SPORT5–0, 12 channels

IDP7–0, 7 channels

SPI – 1 channel

MLB – 31 channels

SPI B – 1 channel

MTM (WR/RD) – 2 channels

UART0(Tx/Rx) – 2 channels

SPORT7–6, 4 channels

Accelerator (In/Out) 2 channels

EPDMA1–0, 2 channels

P1I SPII

P3I SP1I

P4I SP3I

P5I SP5I

P6I SP0I

P7I SP2I

P8I SP4I

P9I EP0I

P11I SP7I

P12I DAILI

P13I EP1I

P14I DPII

P15I MTMI

P16I SP6I

P17I No default

P18I SPIBI Lowest

Loading...

Loading...