External Port DMA Control Registers (DMACx)

A-60 ADSP-214xx SHARC Processor Hardware Reference

External Port DMA Control Registers

(DMACx)

The DMAC0–1 registers control the DMA function of their respective DMA

channels. These registers apply to all processors described in this manual

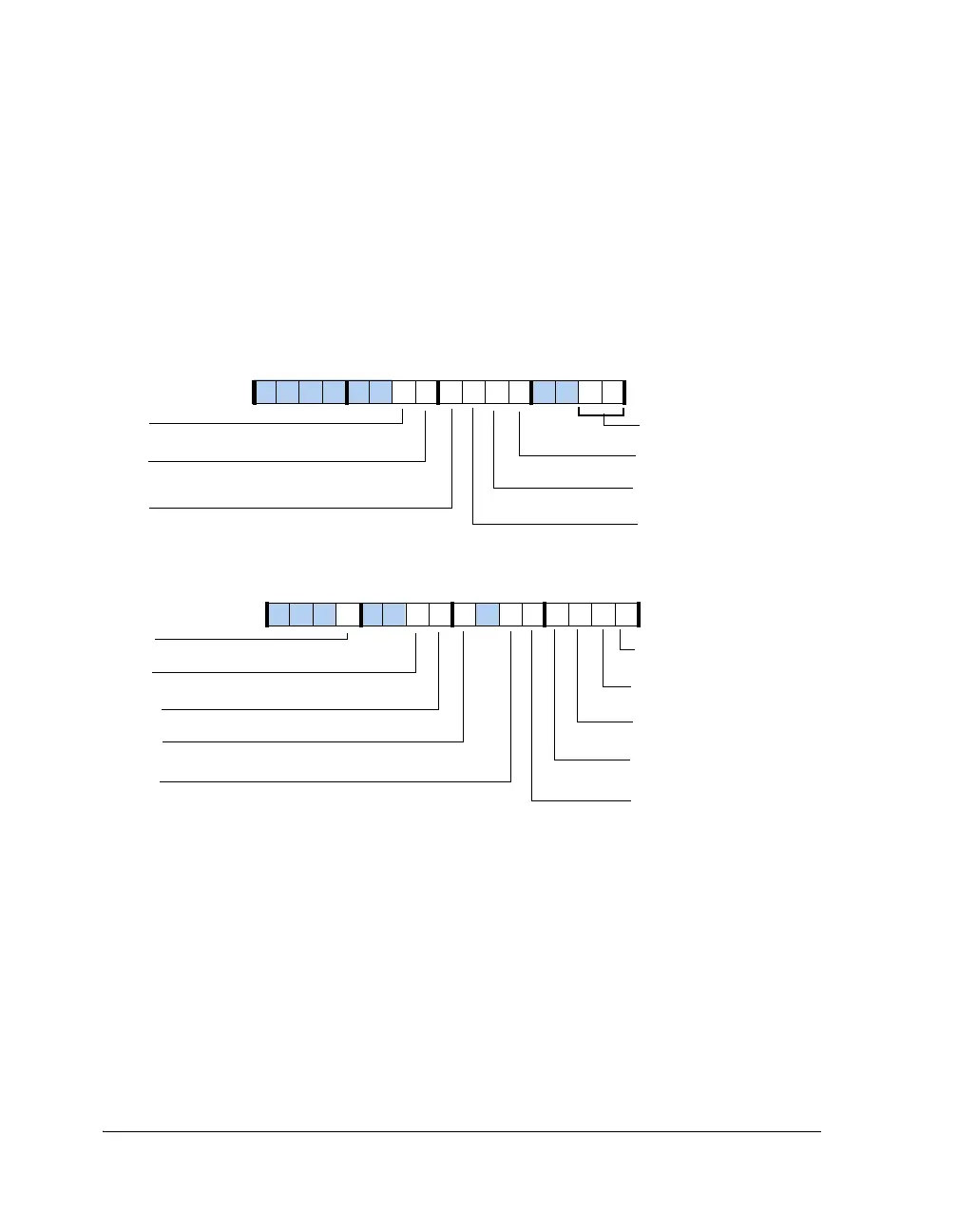

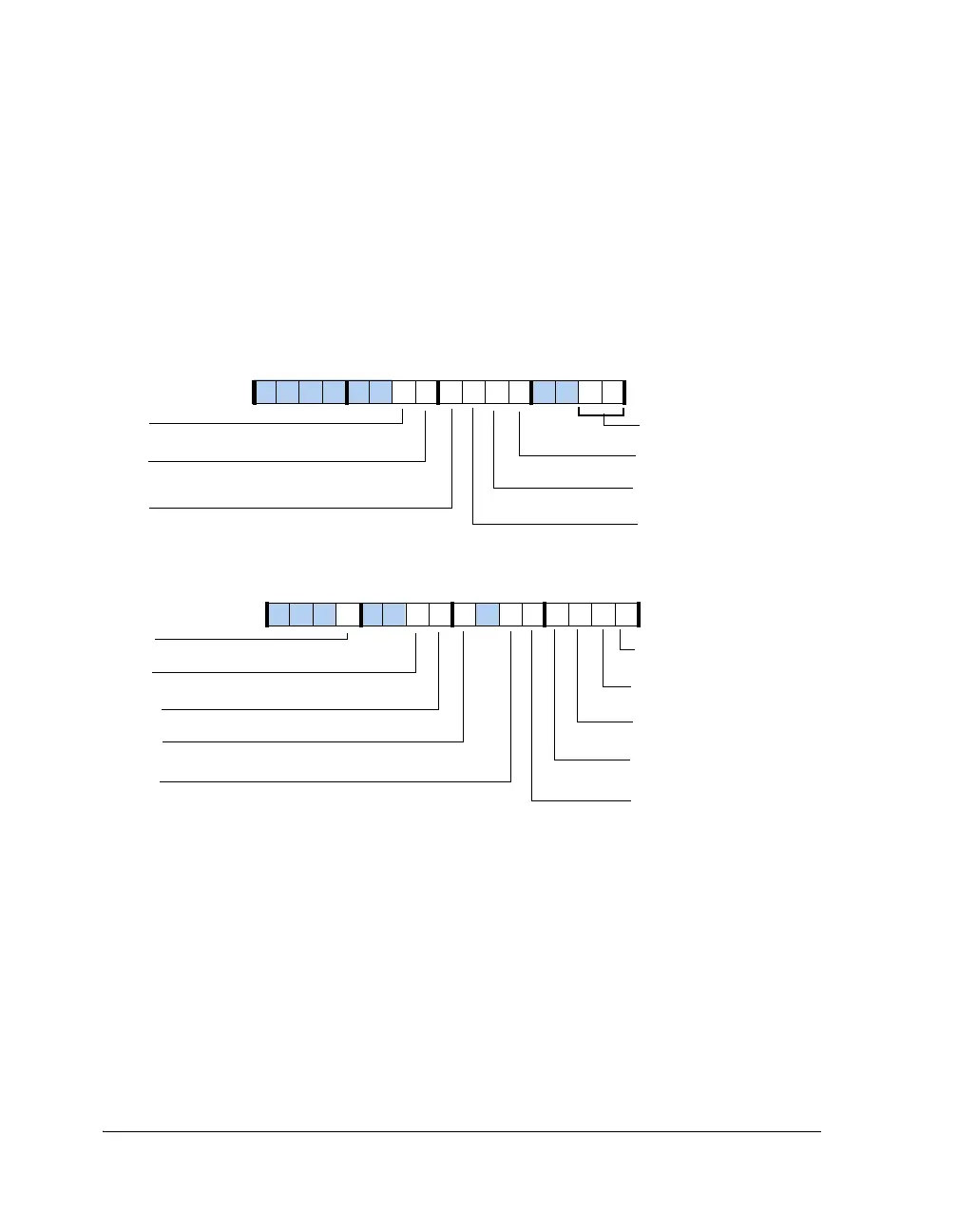

and are shown in Figure A-27 and described in Table A-32.

Figure A-27. DMACx Registers

DEN

EXTS

TLS

Tap List Loading Status

DMAS

DMA Transfer Status

INTIRT

DMA Direction

DMA Enable

CHEN

Chaining Enable

TRAN

DMA FIFO Status

DIRS

DLEN

Delay Line DMA Enable

CBEN

Circular Buffering Enable

DFLSH

Flush DMA FIFO

CHS

DMA Chaining Status

DMA Transfer Direction Status

WBS

Delay Line Write Back Status

DMA External Interface

Status

DFS (17–16)

Internal DMA Completion interrupt (Control)

TLEN

Tap List DMA Enable

OFCEN

On the Fly Control Loading Enable

WRBEN

Enable Write Back of EPEI After Reads/Writes

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

Loading...

Loading...