ADSP-214xx SHARC Processor Hardware Reference A-61

Registers Reference

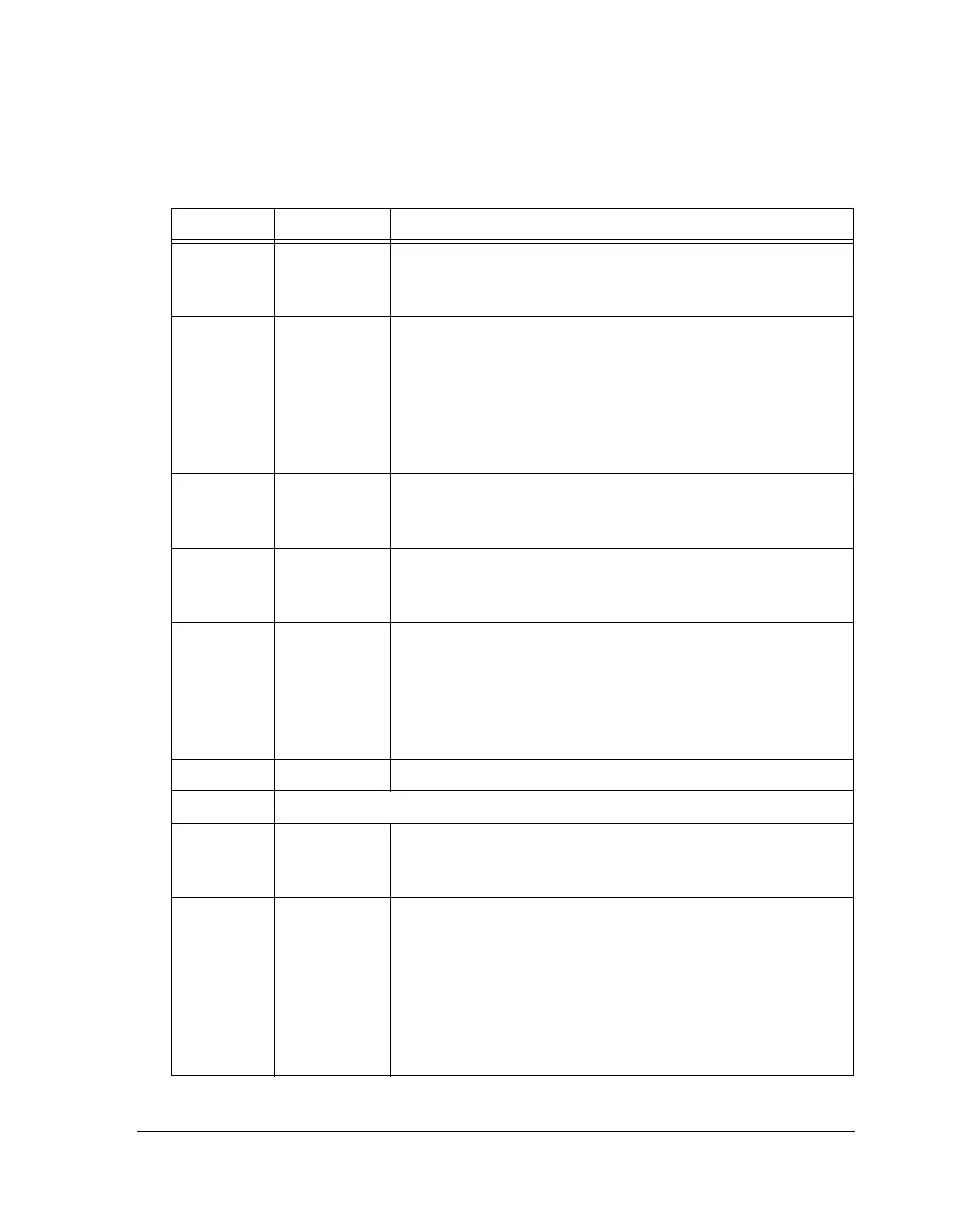

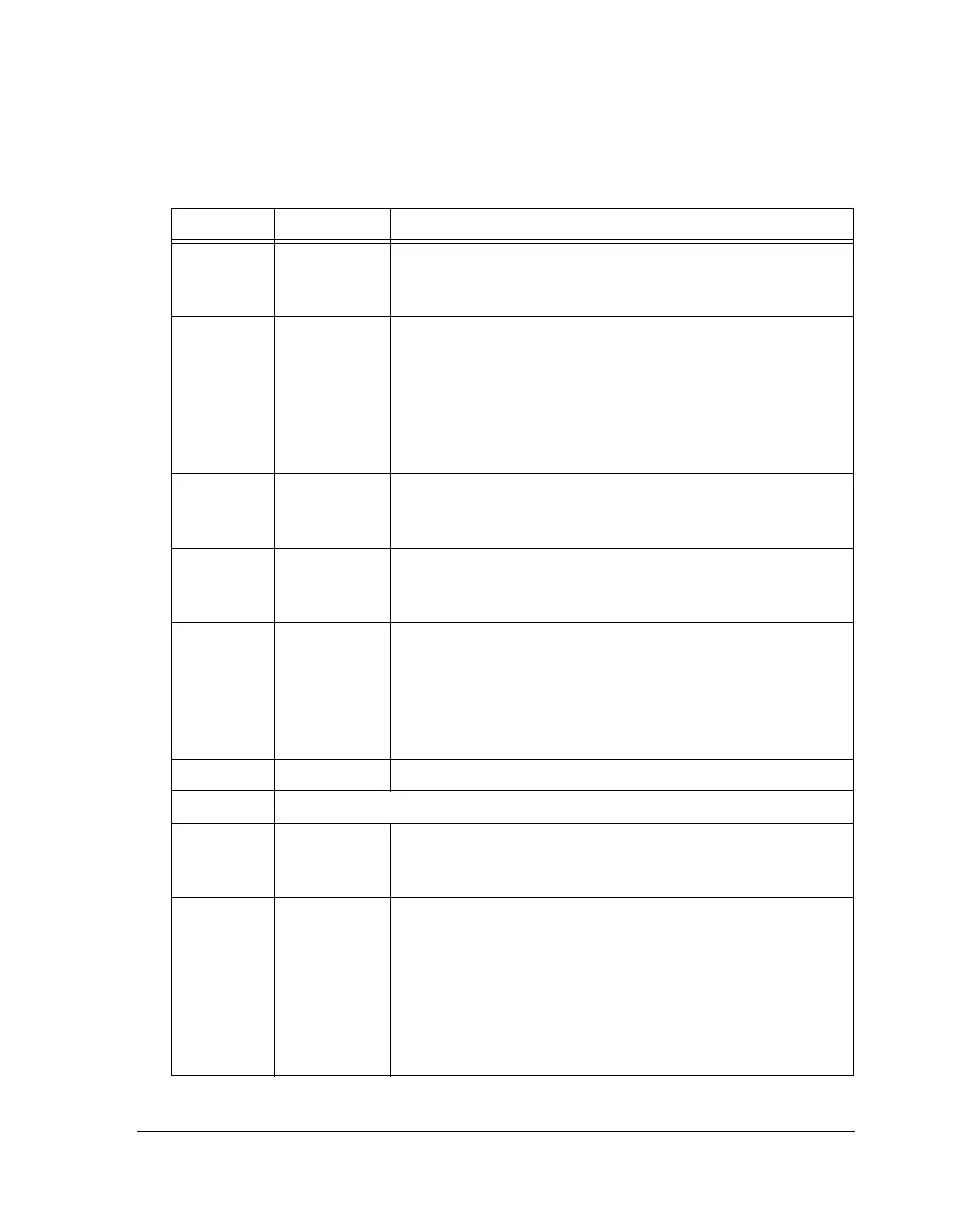

Table A-32. External Port DMA Register Bit Descriptions (RW)

Bit Name Description

0DENDMA Enable.

0 = External port channel x DMA is disabled

1 = Enable External port DMA for channel x

1TRANDMA Direction. Determines the DMA data direction.

For internal to internal transfers, TRAN must be set.

0 = Write to internal memory (external reads)

1 = Read from internal memory (external writes)

Note: If delay line DMA is enabled then the TRAN bit doesn’t

have any effect. For delay line DMA, transfer direction depends

on the state of delay line transfers.

2CHENEnable Chaining.

0 = Chaining disabled

1 = Chaining enabled

3DLENEnable Delay Line DMA. DLEN is applicable only if CHEN=1.

0 = Delay-line DMA disabled

1 = Delay-line DMA enabled

4CBENCircular Buffering Enable.

0 = Disables circular buffering with delay line DMA

1 = Enables circular buffering with delay line DMA

Circular buffering can be used with normal DMA as well, if cir-

cular buffering is enabled with chaining in normal DMA then

ELEP and EBEP should be part of the TCB.

5 (WOC) DFLSH Flush DMA FIFO. Clears the DFS bit.

6 Reserved

7WRBEN Enable Write Back of EIEP After Reads/Writes.

Write back is automatically enabled for Delay Line DMA.

WRBEN is applicable only if CHEN = 1

8OFCENOn the Fly Control Loading Enable.

The control bits in CPEP register are used to describe the next

TCB behavior if OFCEN is set and therefore the DMA controls

can be changed from TCB to TCB.

0 = Disables the control bits in CPEP register

1 = Enables the control bits in CPEP register. Note if chaining is

enabled with OFCEN bit set then TRAN bit has no effect, and

direction is determined by CPD bit in CPEP register.

Loading...

Loading...